TLV32AC56/57音频信号处理器介绍

1 引言

本文引用地址:https://www.eepw.com.cn/article/201808/387674.htmTLV320C56/57是美国TI公司生产的音频处理集成电路(VBAP),它内含发送和接收编译码电路以及发送、接收滤波器,可用于远距离语音通讯、数字信号处理、数字音频处理、数字信号测量等系统和领域。TLV320AC56/57的主要参数如下:

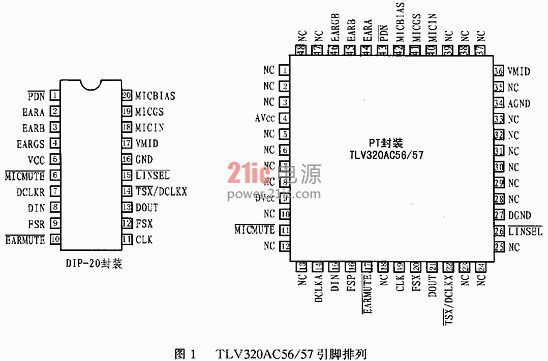

TLV320AC56/57有DIP和PT两种封装形式,图1所示为其引脚排列图。

TLV320AC56/57集成电路有压展和线性两种工作模式。在压展工作模式下,数据的发送和接收均为8位;在线性工作模式下,数据的发送和接收为16位,另3位用于衰减控制,也可填充三个0.

发送部分可直接与驻极体话筒接口,以将话筒信号送给缓冲放大器变固定电平信号,然后再经去噪后送给带通滤波器。在压展工作模式下,滤波器输出信号应送给压展A/D转换器。

接收部分有压展和线性两个D/A转换器,分别用于转换从DIN输入的串行数据。所得的模拟信号送到隔离电容滤波器以滤除带外信号。滤波器同时提供(SinX)/X校正以使信号平滑。其输出信号将直接供给耳机放大器,该放大器的增益是可调的,并能提供低功耗的差分输出。

TLV320AC56/57内有一带隙高精度电源电路,参考电压VMID等于Vcc/2,对放大电路和话筒偏置提供相当于1/2电平的虚地,另一参考电压可为MICBIAS提供话筒的电流偏置。图2是它的功能方框图。

2 引脚功能

下面是TLV320AC56/57的引脚功能说明。其中各引脚后的括号内分别是DIP-20和PT-48脚封装的引脚号,×表示该封装无此引脚。

AGND(×/34脚):所有内部模拟电路地;

AVcc(×/4脚):所有内部模拟线中的3V供电电源;

CLK(11/19脚):时钟输入,在固定比特率的情况下,它可作为主时钟、发送和接收数据的时钟,在可变比特率条件下,CLK仅作主频时钟用;

DCLK(7/14脚):固定或变比特率选择端。DCLK与VCC相连时,选择固定比特率模式;DCLK不与VCC相连时,选择可变比特率模式,这时,DCLK是接收数据时钟;

DGND(×/27脚):所有数据线路的接地端;

DIN(8/15脚):接收数据输入端,在固定比特率模式下,接收数据时钟频率的波形负波时,接收数据输入;

DOUT(13/21脚):发送数据输出端,当发送数据时钟的正半波时发送数据;

DVCC(×/9脚):所有内部数据线路的3V电源;

EARA(2/44脚):耳机输出端,与EARB组成差分驱动输出;

EARB(3/45脚):耳机输出端,与EARA组成差分驱动输出(模拟信号输出);

EARGS(4/46脚):耳机输出增益设置输入端,一个外部电阻电压分配网络联EARA和EARB两端,其电压分配比率决定着功率放大器的增益。当EARGS与EARB相连时,增益最大;EARGS与EARA连接时,增益最小。外接RC网络可校正耳机的频率响应;

EARMUTE(10/17脚):耳机输出静音控制信号输入端,当EARMUTE为低电平时,输出放大器静止,无音频信号输出;

评论