FPD-Link II显示SerDes概述

概述

本文引用地址:https://www.eepw.com.cn/article/201808/387381.htm美国国家半导体嵌入式时钟LVDS SerDes FPD-Link II系列具有强大的功能,超过了前几代FPD-Link SerDes在显示应用上的信号质量。 FPD-Link芯片组将宽并行RGB总线串行化为4或5对LVDS信号。18位RGB串行化为三组LVDS数据线和一个LVDS时钟,而24位RGB则串行化为四组LVDS数据线和一组LVDS时钟。这就提供了一个更小,更高速的视频总线,并成为了笔记本显示接口的实用标准。

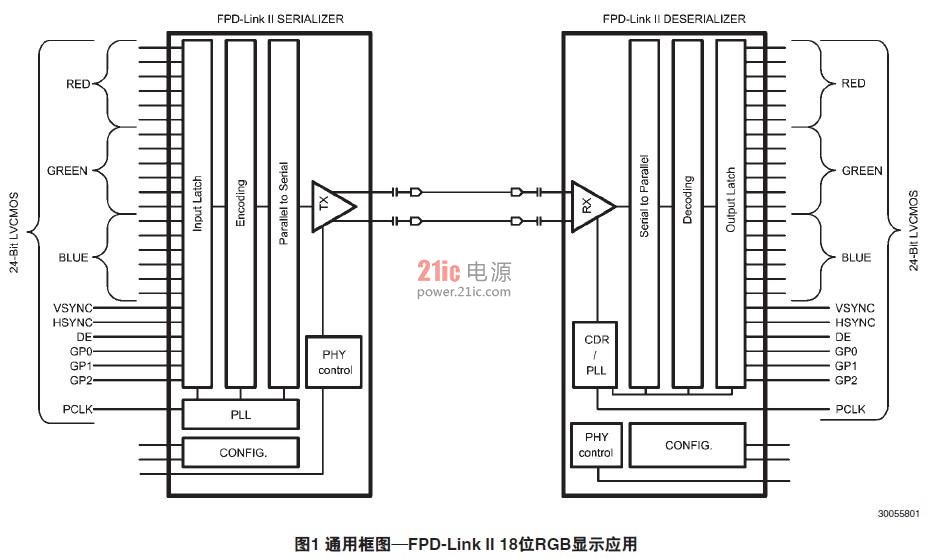

FPD-Link II SerDes系列使宽并行总线串行化为下图1所示的一个串行差分信号。因此获得了24:1或更大的信号压缩比(如果把地线也考虑进来)。系列中的现有芯片支持通用的18位和24位RGB显示应用。由于消除了单串行信号和多线(多路)间的偏差问题,因此支持长达10米的电缆长度。这就使FPD-Link II SerDes理想用于低成本电缆的长距离应用。

单串行差分信号带有并行数据(RGB和控制)信息,时钟信息和小量串行损耗。单信号对的布线大大便利了系统设计,节省了大量互连、接线引脚,并减少了互连接口偏差的忧虑。

点击下载全文PDF资料:FPD-Link II显示SerDes概述

评论