采取强硬路线

作为一个“门海”,FPGA提供了可使用通过各种宽度的查找表来实现逻辑表达式来实现的任何数字功能几乎是无限的平台。自成立以来,这提供了灵活性前所未有的水平,而他们的均匀性和阵列状结构,使他们最新制造节点的早期采用者。

本文引用地址:https://www.eepw.com.cn/article/201808/386790.htm尽管是在不断的半导体技术的前沿,性能还可以在依赖于日益复杂的路由模式和时钟结构的体系结构的限制因素;它是这个原因,厂商先用知识产权(IP)的硬连线块来实现关键功能。

更高的性能和最佳功耗的不竭需求推动FPGA厂商的固定IP的功能越来越多集成到他们的产品。虽然中坚分子可能会认为这是对FPGA技术的核心优势的侵蚀,实际上它提供了访问功能互补,这将是困难或站不住脚的逻辑架构来实现。

其中的核心市场,为高端FPGA一向电信;这里,性能是关键和成本可二次。为了满足这种需求,现在的FPGA整合大量的IP靶向的数据路径,如高速以太网,以及其它串行收发器,以及最近,光接口。这些坐其他性能的关键功能,如PLL和DSP模块的旁边。增加一个软核处理器来处理控制通道功能的能力意味着大的FPGA仍然很受欢迎,在这一领域,往往被优先于ASIC的。

而软核可以解决许多任务,特别是在最新最快的FPGA,它们仍然有限,可能不适合于其他任务,其中的性能是重要的。因此,有点自然,IP集成的扩展看到了引进“硬”处理器内核;已经采取了多次迭代完全实现,但现在做的许多应用领域一个显著影响的概念。

早期尝试嵌入硬核处理器在FPGA中未能激发行业或革命性的技术:太多了,太快了,也许吧。该行业整体回落的软核选项,但它很快变得清晰,真的是市场的嵌入式处理器;它只是需要合适的解决方案。可以说,这竟然是ARM。

今天,有许多的FPGA均提供嵌入式ARM内核,以及软核选项,并说明理由很清楚;业绩保证。此外,延长硬核硬件加速FPGA架构的能力开辟了更加的应用领域,其中FPGA供应商现在热衷于探索。

该SoC

从概念上讲,FPGA供应商是指逻辑结构和硬IP的集成为一个系统级芯片(SoC)方案,由处理器厂商谁整合等功能广泛使用的一个术语。这包括处理器,提供可配置逻辑,如PSoC系列从赛普拉斯。在性能方面,嵌入式处理器子系统是不是只为非常高端的; Altera公司现在提供其高性能Stratix,其中档阿里亚和低成本Cyclone系列基于ARM的SoC解决方案。

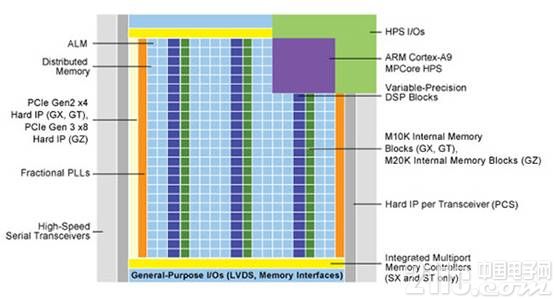

从系统的水平,在FPGA中列入一个处理器子系统并不需要在物理上它主宰。图1显示了Altera的阿里亚伏,这清楚地显示了基于ARM的Cortex-A9 MPCore的子系统占用在硅中只有一小部分的硬处理器系统(HPS)的表示。这反映在图2中,低成本Cyclone伏,还集成了高压钠灯的方框图。

Altera的阿里亚V族图片

图1:Altera的阿里亚V族中档功能的SoC厂商硬核处理器系统(HPS)。

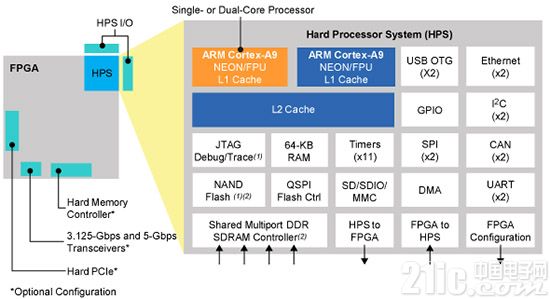

Altera的低成本Cyclone V影像

图2:Altera的低成本Cyclone五还配备了高压钠灯,要么提供的单核或双核的ARM Cortex-A9子系统的旁边FPGA架构。

在这种配置中,每个核心包括32-K字节的L1指令缓存和32 KB的L1数据高速缓存,单精度和双精度浮点单元和NEON媒体引擎,CoreSight调试和跟踪的。还有一个512 KB的共享L2缓存也被集成,以及64K字节的RAM划伤。内存和通用接口,提供一系列包括 - 多达134个通用I / O。重要的是,HPS和FPGA能够独立运作,而是通过使用ARM的AMBA AXI总线桥,这给HPS访问FPGA架构,反之亦然建成了高带宽系统互连保持紧密耦合。这两个桥是AMBA AXI-3标准。一个专用32位配置端口允许的HPS配置FPGA在启动。

一个主题变奏曲

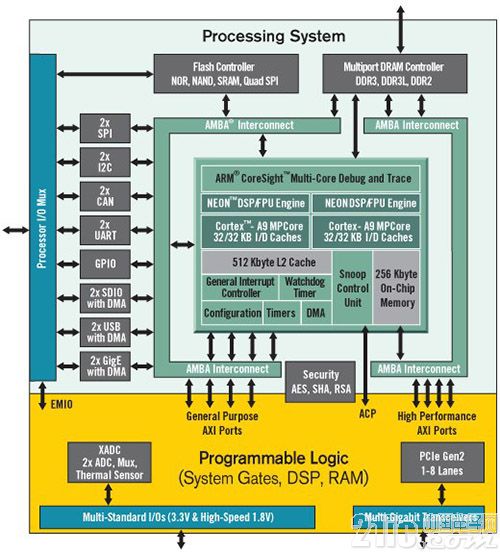

类似的Altera,赛灵思还采用了双核的ARM Cortex-A9 MPCore的子系统方法对它的SoC产品,但不像它的竞争对手,而不是支持三个家庭在不同的性能/价格点,它的选择实施一系列表现跨一个家庭的水平;在ZYNQ-7000。

图3:ZYNQ-7000系列赛灵思还提供了一个双核的ARM Cortex-A9子系统提供一系列的FPGA架构的密度选项。

像Altera的Cyclone V,ZYNQ-7000还支持全或部分重新配置,使得在FPGA的一部分,以继续运行,而剩余的部分被重新配置,而无需停止整个系统。处理器子系统还能够独立地对FPGA的逻辑运行。

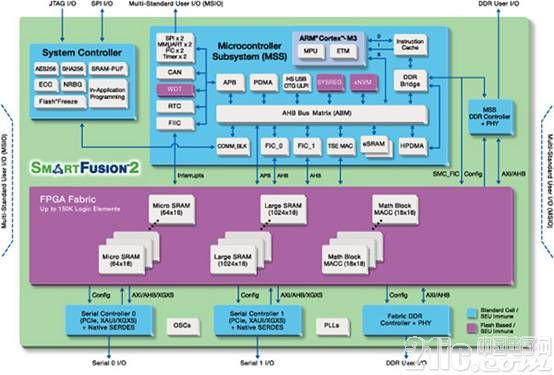

而前面的两个例子使用“经典”的SRAM的方法来对FPGA织物,这就需要在上电时将其配置数据加载,也有SoC器件集成的硬核处理器基于Flash的例子提供更多的'瞬时接通“用例,如SmartFusion2家族从Microsemi的。

图4:Microsemi的SmartFusion2 SoC的FPGA框图。

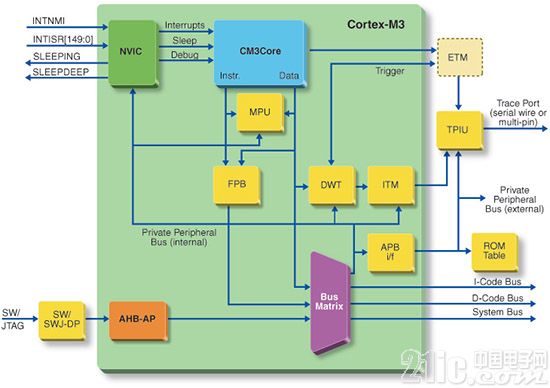

图5:Microsemi的SmartFusion2的ARM Cortex-M3的子系统。

不像这里的特色其它系统芯片,该SmartFusion2家庭解决真正的低功耗,明显由Cortex-M3内核,这主要是与微控制器应用相关的选择,而不是在Cortex-A类由Altera和Xilinx,这是受宠更适合于应用处理器类型使用情况。在这种集成水平,SmartFusion2开始像通常不认为是其他的FPGA解决方案,如在PSoC 5系列从赛普拉斯;然而,高达15万个逻辑单元的FPGA架构,该SmartFusion2家庭保留其FPGA凭据。

结论

的FPGA和处理器核心技术的融合有一个漫长而多事的历史。初步显示出小许的时候,可能在被注销完全的危险。幸运的是,所有的开发人员来说,FPGA厂商表现出远见的水平,确保它的复兴,通过软核的成功显著帮助。

现在,嵌入式硬核被牢牢解决方案的工程师'工具箱'嵌入'和许多应用程序是否真能代表一个完整的系统级芯片。它不会停在那里:Altera公司已经宣布其新一代的Stratix系列10将集成4个64位ARM Cortex-A53内核,采用英特尔三栅极技术构建,给它真正的无与伦比的性能水平。

喜欢它的过去,它看起来像FPGA的SoC的未来将是多么不平凡的,但可能更加成功。

评论