并行总线与串行总线

虽然随着技术的发展,现代的数字芯片已经集成了越来越多的功能,但是对于稍微复杂一点的系统来说,很多时候单独一个芯片很难完成所有的工作,这就需要和其它芯片配合起来工作。比如我们现在的CPU的处理能力越来越强,很多CPU内部甚至集成了显示处理的功能,但是仍然需要配合外部的内存芯片来存储临时的数据、需要配合桥接芯片扩展硬盘、USB等外围接口;现代的FPGA内部也可以集成CPU、DSP、RAM、高速收发器等,但有些场合可能还需要配合专用的DSP来进一步提高浮点处理效率、配合额外的内存芯片来扩展存储空间、配合专用的物理层芯片来扩展网口、USB等,或者需要多片FPGA互连来提高处理能力。所以的这一切,都需要用到相应的总线来实现多个数字芯片间的互连。如果我们把各个功能芯片想象成人体的各个功能器官的话,总线就是血脉和经络,通过这些路径,各个功能模块间才能进行有效的数据交换和协同工作。

本文引用地址:https://www.eepw.com.cn/article/201807/383770.htm我们经常使用到的总线根据数据传输方式的不同,可以分为并行总线和串行总线。

并行总线:

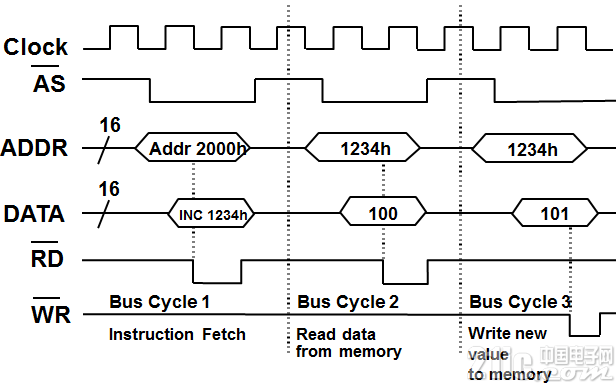

并行总线是数字电路里最早也是最普遍采用的总线结构。在这种总线上,要传输的数据线、地址线、控制线等都是并行传输,比如要传输8位的数据宽度,就需要8根数据信号线同时传输,如果要传输32位的数据宽度就需要32根数据信号线同时传输。除了数据线以外,如果要寻址比较大的地址空间,还需要很多根地址线的组合来代表不同的地址空间。下图是一个典型的微处理器的并行总线的工作时序,其中包含了1根时钟线、16根数据线、16根地址线以及一些读写控制信号。

很多经典的处理器都采用了并行的总线架构。比如大家熟知的51单片机就采用了8根并行数据线和16根地址线;CPU的鼻祖,Intel 公司的8086微处理器最初推出时具有16根并行数据线和16根地址线;现在很多嵌入式系统中广泛使用的ARM处理器则大部分使用32根数据线以及若干根地址线。

并行总线的最大好处是总线的逻辑时序比较简单,电路实现起来比较容易,但是缺点也是非常明显的。比如并行总线的信号线数量非常多,会占用大量的管脚和布线空间,因此芯片和PCB板的尺寸很难实现小型化,特别是如果要用电缆进行远距离传输时,由于信号线的数量非常多,使得电缆变得非常昂贵和笨重。

采用并行总线的另外一个问题在于总线的吞吐量很难持续提升。对于并行总线来说,其总线吞吐量=数据线位数×数据速率。我们可以通过提升数据线的位数来提高总线吞吐量,也可以通过提升数据速率来提高总线吞吐量。以个人计算机里曾经非常流行的PCI总线为例,其最早推出时总线是32位的数据线,工作时钟频率是33MHz,其总线吞吐量=32bit×33MHz;后来为了提升其总线吞吐量推出的PCI-X总线,把总线宽度扩展到64位,工作时钟频率最高提升到133MHz,其总线吞吐量=64bit×133MHz。下图是PCI插槽和PCI-X插槽的一个对比,可以看到PCI-X由于使用了更多的数据线,其插槽更长(来源:网络图片)。

但是随着人们对于总线吞吐量的要求的不断提高,这种提升总线带宽的方式遇到了瓶颈。首先由于芯片尺寸和布线空间的限制,64位数据宽度已经几乎是极限了。另外一方面,这64根数据线是共用一个采样时钟,为了保证所有的信号都满足其建立保持时间的要求,在PCB上布线、换层、拐弯时需要保证精确等长。而总线工作速率越高,对于各条线的等长要求就越高,对于这么多根信号要实现等长的布线是很难做到的。

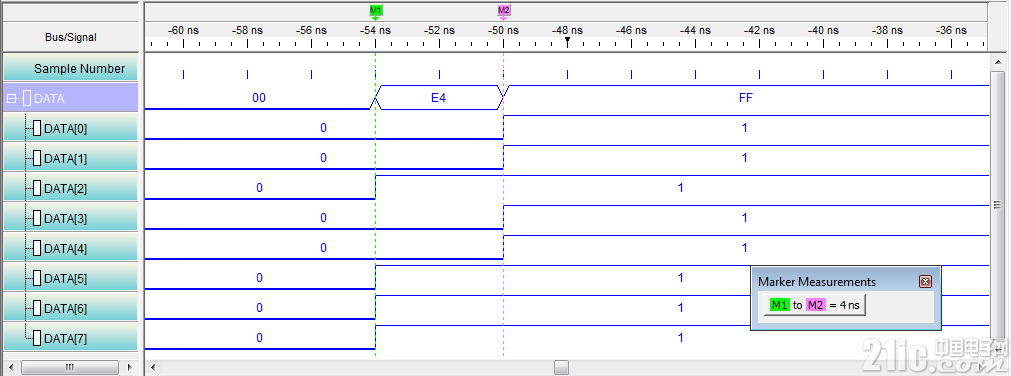

下图是用逻辑分析仪采集到的一个实际的8位总线的工作时序,我们可以看到在数据从0x00跳变到0xFF状态过程中,这8根线实际并不是精确一起跳变的。

对于并行总线来说,更致命的是这种总线上通常挂有多个设备,且读写共用,各种信号分叉造成的反射问题使得信号质量进一步恶化。

串行总线:

为了解决并行总线占用尺寸过大且对布线等长要求过于苛刻的问题,随着芯片技术的发展和速度的提升,越来越多的数字接口开始采用串行总线。所谓串行总线,就是并行的数据在总线上不再是并行地传输,而是时分复用在一根或几根线上传输。比如在并行总线上传输1个Byte的数据宽度需要8根线,而如果把这8根线上的信号时分复用在一根线上就可以大大减少需要的走线数量,同时也不需要再考虑8根线之间的等长关系。

采用串行总线以后,就单根线来说,由于上面要传输原来多根线传输的数据,所以其工作速率一般要比相应的并行总线高很多。比如以前计算机上的扩展槽上广泛使用的PCI总线采用并行32位的数据线,每根数据线上的数据传输速率是33Mbit/s,演变到PCI-E(PCI-Express)的串行版本后每根线上的数据速率至少是2.5Gbit/s(PCI-E 1代标准),现在PCI-E的数据速率已经达到了5Gbit/s(PCI-E 2代标准)或8Gbit/s(PCI-E 3代标准)。采用串行总线的另一个好处是在提高数据传输速率的同时节省了布线空间,同时芯片的功耗也降低了,所以在现代的电子设备中,当需要进行高速数据传输时,使用串行总线的越来越多。

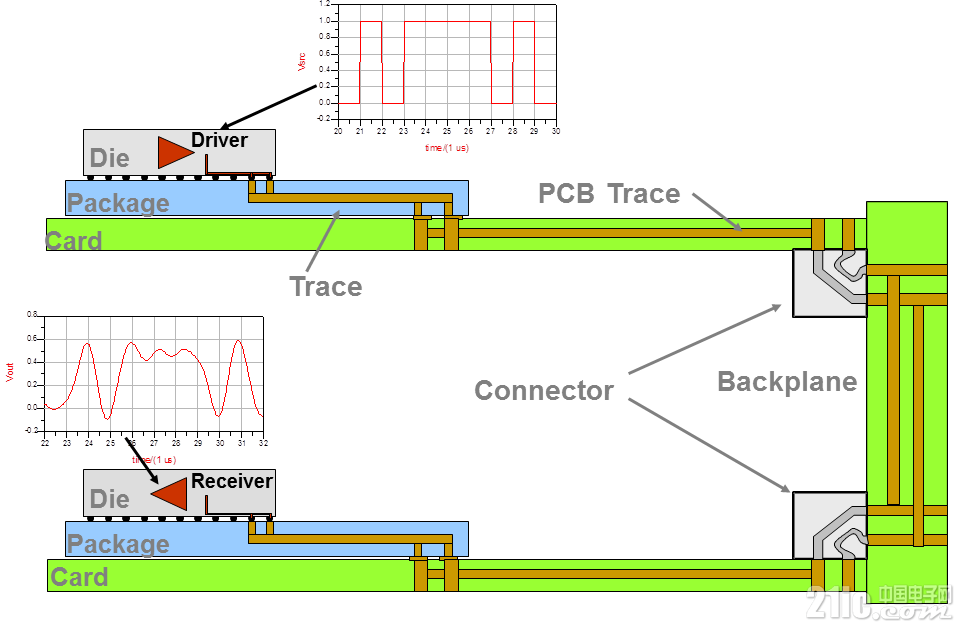

数据速率提高以后,对于阻抗匹配、线路损耗和抖动的要求就更高,稍不注意就很容易产生信号质量的问题。下图是一个典型的1Gbps的信号从发送端经过芯片封装、PCB板、连接器、背板传输到接收端的信号路径,从中我们可以看到在发送端的接近理想的0、1跳变的数字信号到达接收端后由于高频损耗、反射等的影响信号波形已经变得非常恶劣,所以串行总线的设计对于数字电路的工程师来说是个很大挑战。

使用串行总线的设备的体积、功耗和数据传输速度都比使用并行接口的设备更有优势,因此得到了广泛的应用。比如以前在计算机上广泛使用的连接打印机的DB25的并口已经被USB和网口取代,以前连接硬盘的40pin的PATA接口已经被串行的SATA接口取代,以前计算机上的PCI扩展槽已经被PCI-Express取代。但是如前所述,采用串行总线以后信号的数据速率一般都会有几倍甚至几百倍的提升,对于电路的设计和测试都提出了很高的要求,因此需要设计和测试工程师掌握大量的高速设计的相关知识和技能。

评论