让下一代智能互联嵌入式应用开发更简化

Cortex-M处理器家族是一系列具有扩展性,兼容性,节能和易于使用的处理器,旨在帮助开发人员满足未来智能互联嵌入式应用的需要。2010年推出的Cortex-M4是建立在Cortex-M3的基础上并加入了一系列专门为数字信号处理定制的指令集扩展,并搭配可选的性能可达1.25 DMIPS/ MHz的单精度浮点单元。自推出以来,有10家以上的半导体厂商推出了基于Cortex-M4的通用MCU产品,以及非常广泛的基于Cortex-M4的sensor hub产品。

本文引用地址:https://www.eepw.com.cn/article/201807/383691.htm在过去的几年里,对支持互联的嵌入式系统的功能特性和处理能力的需求变得更加苛刻。即使是最简单的系统,也预期支持多种连接方式,图形用户界面,人机界面,语音识别或其他自然的交互方式。处理器需要变得更加强大,并能提供更多的本地处理能力。在汽车行业和工业自动化中应用的微控制器需要支持更高的处理能力和CPU性能提升,对计算精度和短时间内处理大量数据的要求在迅速提高。这些未来系统的要求包括:以较低的成本提供更多的功能,增加连接性,更好的代码重复利用,以及提高能效。正是着眼于这样的未来需求,ARM和合作伙伴一起设计了当前Cortex-M家族中性能最强的ARM Cortex-M7处理器。

近观Cortex-M7

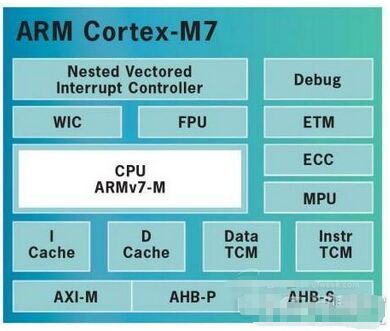

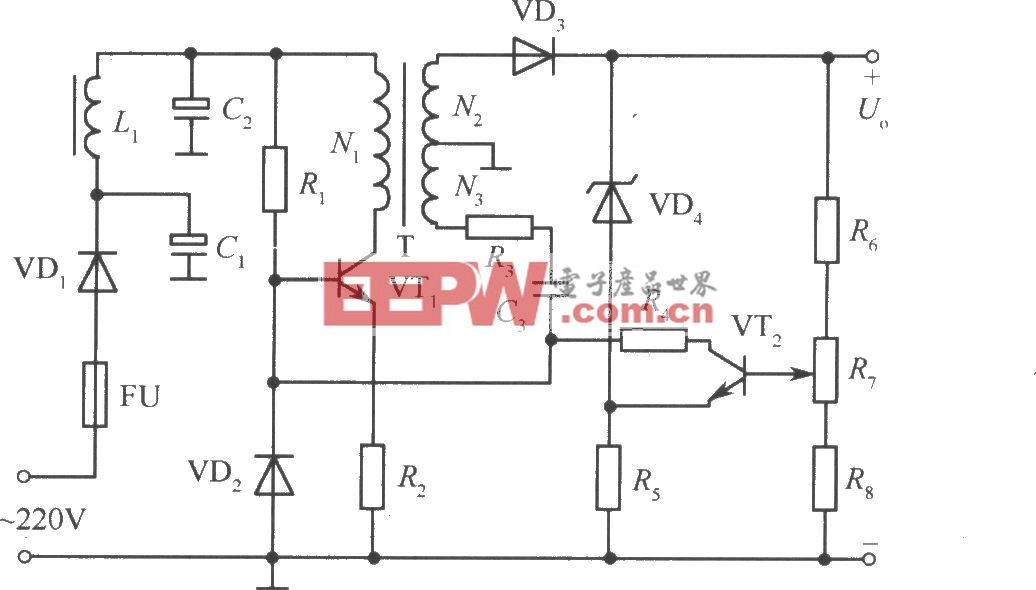

Cortex-M7能够应对最严格的应用环境,并克服了以前基于Cortex-M处理器的解决方案所面临的问题,性能达到了上一代Cortex-M4的两倍,大约为5 CoreMark/ MHz。Cortex-M7是专为各种嵌入式应用,包括微控制器,汽车控制器,工业控制系统和无线通信控制器(例如无线网络)设计的。对于那些熟悉Cortex-M系列CPU的嵌入式应用开发者来说,Cortex-M7基于Cortex-M架构,从架构上兼容从Cortex-M0以来的所有产品(图1)。

图1

ARM Cortex-M7处理器特性

Cortex-M7包含六阶段的超标量流水线,并和紧耦合内存、高速缓存和大内存支持选项集成在一起以提供整数、浮点和DSP处理能力并保证确定性的行为。Cortex-M7先进的流水线能提供相对于Cortex-M4更高的性能,允许在每个时钟周期执行两条指令。

Cortex-M7开发的一大重点是相对于之前的Cortex-M系列处理器提高IPC(instructions-per-clock)效率。Cortex -M7是Cortex-M家族中第一个提高最高64KB指令和数据缓存选项的处理器,高速缓存能提供对更大的存储器系统的有效操作(外存通常比处理器慢很多)。此外还添加了紧耦合内存接口,集成ECC支持。对内存的快速访问使得高速中断处理和实时应用处理成为可能。这样的集成使得工程师们可以在内部缓存中执行大部分代码,以减少对外部存储器读写访问,从而降低功耗。

Cortex-M7也提供了对每个内部缓存单元增加ECC支持的选项,以提高系统的可靠性。对于给定解决方案,如果某个内存位置的单个比特值被破坏,该数据可被校正和恢复。除了ECC,存储器系统也可以通过可选的存储器保护单元(MPU)设定8或16个区域为受保护区域以增强系统可靠性。

为了支持提高了的CPU处理能力,内存系统也从32位AXI总线改进为64位AXI总线,64位AXI比32位AXI提供了更大的带宽,并支持多个outstanding transfer以最大化系统性能。为了易于集成在先前的Cortex-M设计中使用的传统外围设备,还有一个可选的低延迟AHB外设总线接口。为了允许灵活的中断管理和低中断延迟,集成嵌套矢量中断控制器(NVIC)用1到240个中断,以及3至8位可编程优先级寄存器实现与处理器的紧密集成。此外,还有ETM支持,专为CoreSight(ARM支持全系统调试和跟踪的架构)设计。

Cortex-M7包含的双精度支持可选项,进一步扩大了Cortex-M家族的浮点能力。如果FPU存在时,还支持整数和浮点指令的并发。鉴于存在大量基于Cortex-M7的MCU应用,它还具有完全的强大的调试功能,以及可选的全指令和数据跟踪支持。对已经使用了Cortex-M4处理器的设备,在应用对性能的要求提高时,前述特性使得Cortex-M7成为一种极具吸引力的解决方案。

迁移设计到Cortex-M7

鉴于大多数嵌入式工程师和开发人员都熟悉Cortex-M4,让我们来看看Cortex-M7带来的一些软件开发的优点。从开发者的角度来看,在Cortex-M7支持所有的Cortex-M4处理器指令,并使用相同的中断模型来处理异常。在大多数情况下,针对Cortex-M4处理器编写的程序代码应该可以在Cortex-M7处理器上没有任何问题地运行。但是,在有些情况下可能需要做一些改动,软件开发人员必须了解这些改动以减少把应用程序从Cortex-M4迁移到Cortex-M7所需的时间。

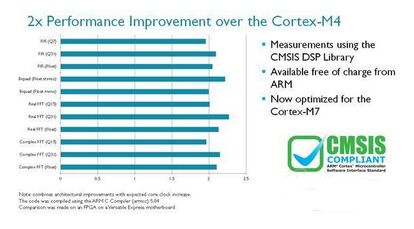

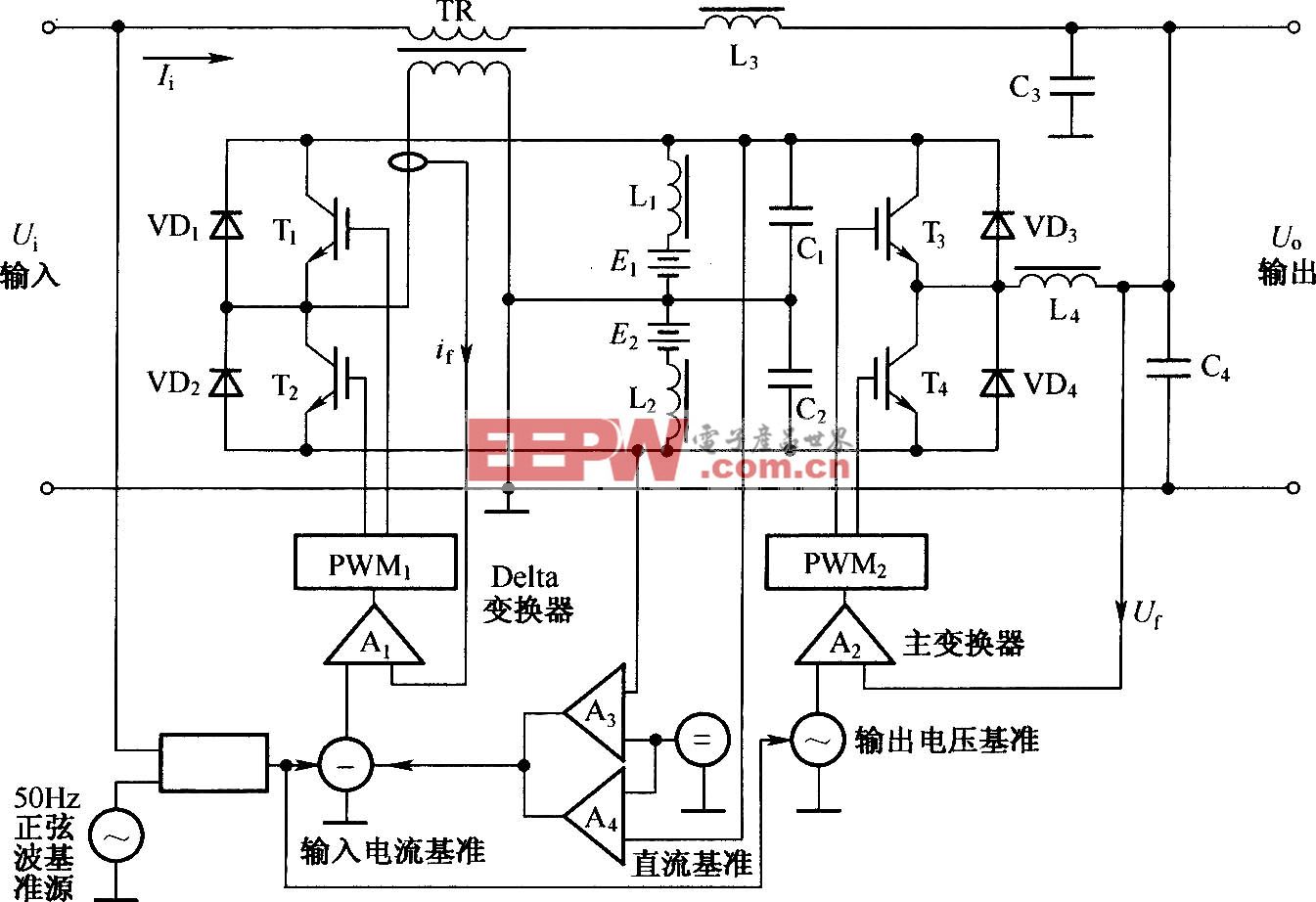

为了获得Cortex-M7处理器的最佳性能,一些C编译器和运行时库已经进行了优化和更新(图2)。此外,由于相当多的Cortex-M7相对于Cortex-M4在调试系统上的变化,软件开发者必须更新他们的工具链,以在基于Cortex-M7的微控制器产品上调试应用程序。在某些情况下,调试适配器上的固件可能还需要更新。因此,强烈建议更新到最新的开发工具链。

图2

相对于Cortex-M4的2倍性能改进

通常情况下,把软件从Cortex-M4迁移到Cortex-M7处理器时,需要完成以下改动:

(1)、更新CMSIS- CORE头文件为Cortex-M7对应的头文件。对应Cortex-M7处理器的CMSIS-CORE头文件包含在CMSIS 4.2之后的版本中。(最新的CMSIS可以从www.arm.com/cmsis获得。)

(2)、更新CMSIS-DSP库为Cortex-M7定制版本。Cortex-M7定制版本为Cortex-M7处理器的流水线行为进行了优化,因此可以提供更高的性能。

(3)、进行缓存配置的新API包含在CMSIS-CORE头文件中。如果正在使用的Cortex-M7装置经由AXI接口从慢速存储器(例如Flash)执行程序,应该启用高速缓存以获得更好的性能。

此外,所有的代码应该被重编译以允许编译器针对Cortex-M7处理器流水线更好地优化指令序列。在某些情况下,可能在运行时需要额外的缓存维护操作。例如,在处理器和外设DMA控制器共享一块带缓存的内存时,必须进行适当的缓存维护操作以保证内存一致性。

评论