工程师不得不懂的MCU混合信号验证策略和挑战

摘要:

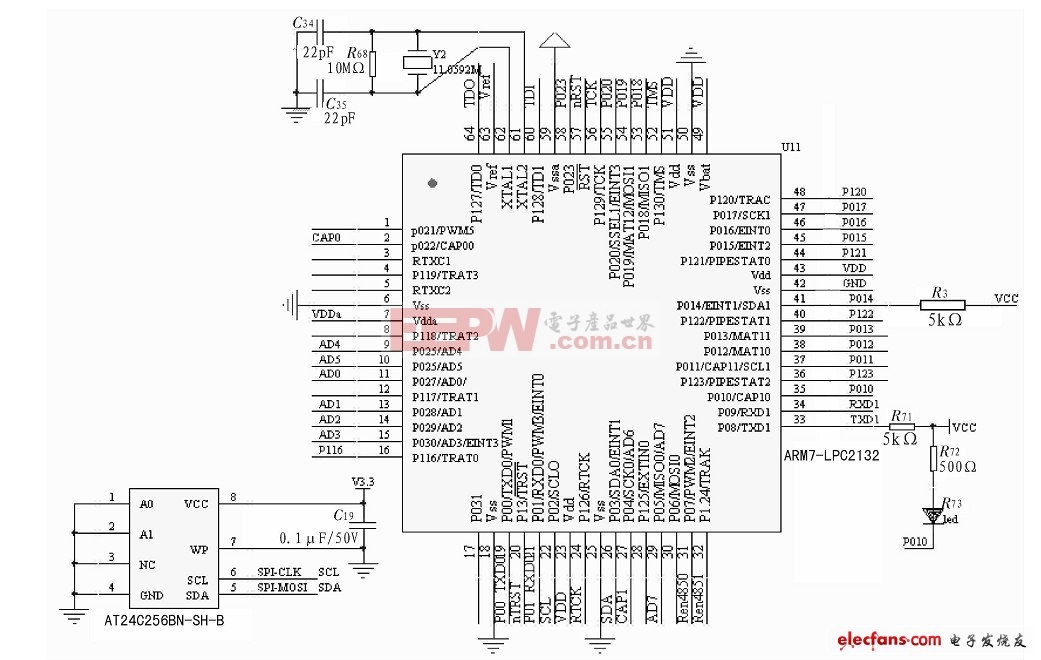

飞思卡尔Kinetis MCU系列是一款高度集成、低功耗32位微处理器,基于ARM Cortex M4内核并拥有面向工业控制和多市场业务的内置DSP功能。Kinetis MCU采用Cadence模拟混合信号验证平台。本文将主要介绍Kinetis MCU混合信号的验证策略和挑战,其中包括混合信号建模、连接验证、混合信号VIP、混合信号功率验证和混合信号覆盖范围。

1 介绍

飞思卡尔Kinetis MCU系列是一款高度集成、低功耗32位微处理器,基于ARM Cortex M4内核并拥有面向工业控制和多市场业务的内置DSP功能。该产品是一大创新成果,是飞思卡尔迈出的重要一步。

Kinetis拥有多个复杂的混合信号IP。这些IP拥有多种不同的模式和设置,可支持多个电源。模拟部分可与数字部分以及其他模拟设计紧密合作。从模拟IP的角度来看,与性能需求相比,该IP功能变得越来越重要。从片上系统的角度来看,由于设计复杂,很难发现隐藏的错误。

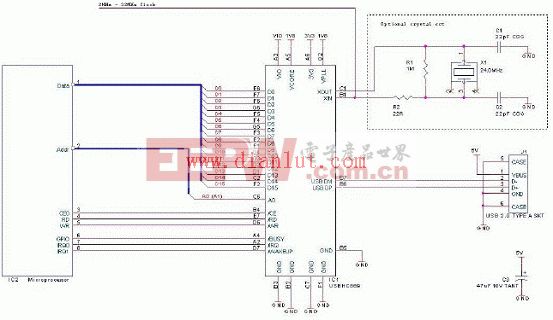

鉴于以上几点,kinetis产品采用了最新的数模混合信号验证方法学。Verilog-AMS语言为模拟IP建模,采用了Cadence AMS designer验证平台进行仿真。

本文包括4部分:第一部分为背景介绍,第二部分为Kinetis MCU混合信号验证方法概述,第三部分为Kinetis MCU混合信号验证在AMS建模、AMS VIP、连接性验证、功率验证和AMS覆盖范围所面临的挑战。

2 设计与实施

2.1 AMS Designer

Cadence Virtuoso® AMS Designer是一款灵活的混合信号模拟器,它可以连接高级模拟和数字环境,从而实现无缝的混合信号模拟和验证。它将数字NC-Sim引擎与4款流行的MMSIM模拟引擎(Spectre、SpectreRF、APS® 和UltraSim®)相结合。根据设计特性,为设计人员提供他们所需的仿真结果。

AMS designer集成了面向混合信号验证的Virtuoso全定制环境和面向在数字验证环境中的用于混合信号验证的Cadence敏捷型功能验证平台。它可支持向下算法,从而在早期设计周期中迅速检测到设计错误,并采用混合信号硬件描述语言来加快仿真速度。

2.2混合信号验证的策略和方法

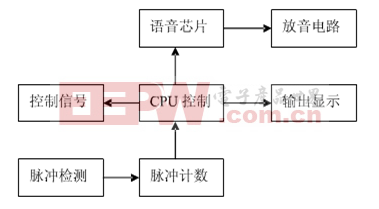

验证采用了软硬件协同仿真方法

SoC测试平台是建立在基于C语言的定向测试案例、??基于系统Verilog的测试平台组件,基于Verilog-AMS的测试平台组件和基与system verilog的随机约束激励。验证方法包括形式验证、基于断言的验证、覆盖驱动的随机约束验证方法。

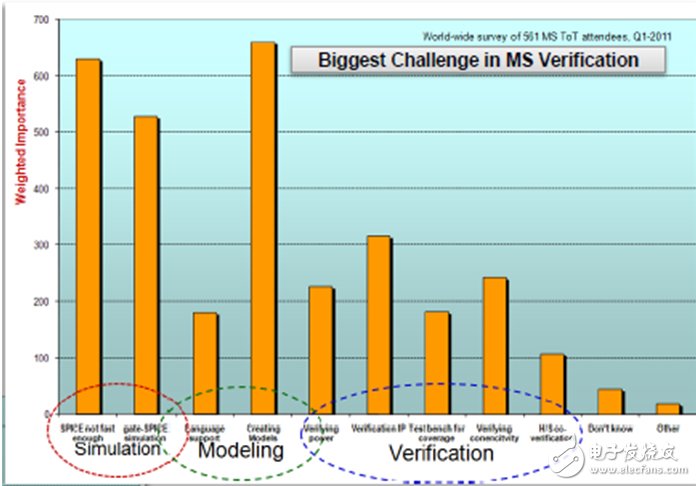

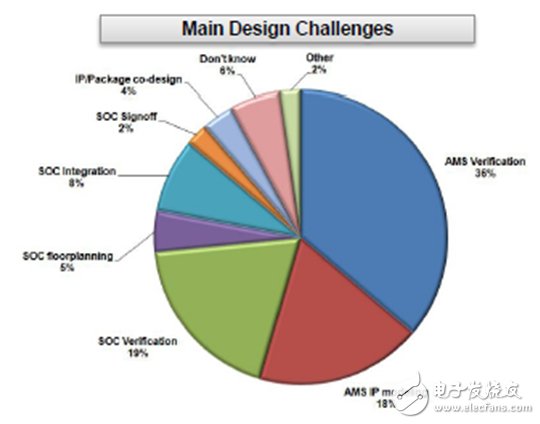

2.3混合信号验证的挑战

在所有主要的设计挑战中,混合信号验证是最大的一个。对于绝大部分的芯片故障,大部分都是可以通过更好的验证方法预防的。那么混合信号验证最大的挑战是什么?就是AMS建模、功耗验证、验证IP、连通性验证、H/S协同仿真和覆盖率。接下来将会详细介绍Kinetis混合信号验证是如何克服这些挑战的。

2.3.1 混合信号验证的挑战之一 – 行为建模

AMS建模有一个共同的规则----建你所需要的模型,而不是你能建的模型。

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处。

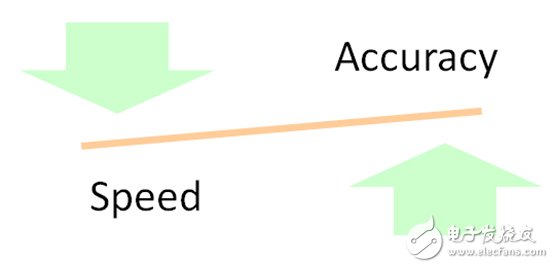

永远要平衡仿真的速度和精度。

有一些关于模型创建的简约、精确、性能和可读的若干准则。

·简约,只针对必要的功能验证建模。要在简约和精确之间进行权衡,这需要写模型的人、模拟设计人员和验证工程师讨论决定。应考虑到验证要求和意图。

·精确:不能精确表示电路行为的模型可能导致错误被疏忽。精确的建模所有数字逻辑是很重要的。模型应该根据存在/不存在适当的偏置电压/电流和电源来启动/停止操作。

·性能:AMS模型可能对仿真器性能产生负面影响。写模型的人需要考虑仿真速度。

·可读:模型很可能是其他模型的起点,所以要创建可读的代码,提供清楚的注释是很重要的。

2.3.2 混合信号验证的挑战之二 – 连接性验证

混合信号的第二大挑战是连接性验证。

混合信号验证往往会发现三种类型的功能性错误。

实施许多设置的单个模拟模块。 这些错误通常是控制逻辑上的微妙问题。设计者如果有太多的设置要测试,就很难发现。

连接性验证的重点在模拟到模拟接口或数字到模拟接口上。大多情况下有两种连接性错误:

1. 模块间通信错误;这属于鸡生蛋蛋生鸡的问题。举例来说,低功率芯片上调节器依赖于共享偏置发生器的情况。如果偏置发生器本身依赖于调节器的输出,那么这对组合可能永远都无法启动。

2. 数字电路,控制模拟,产生其输入,或处理其输出;或者是模拟和数字电路之间的接口。

大多数连接都有直接激励和检查器,对各个模拟模型来说,所有的输入都直接传送为输出。

特殊情况下,应当应用基于断言的验证方法用于连接性验证。

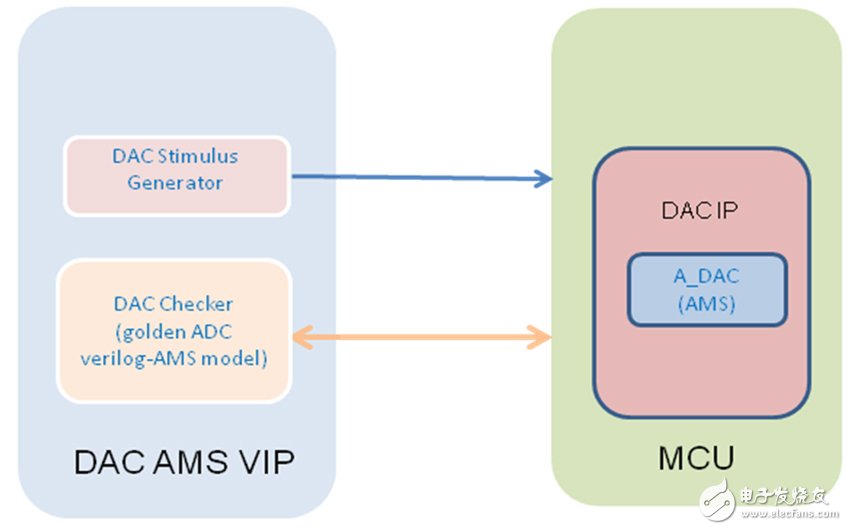

2.3.3 混合信号验证的挑战之三 – 验证IP

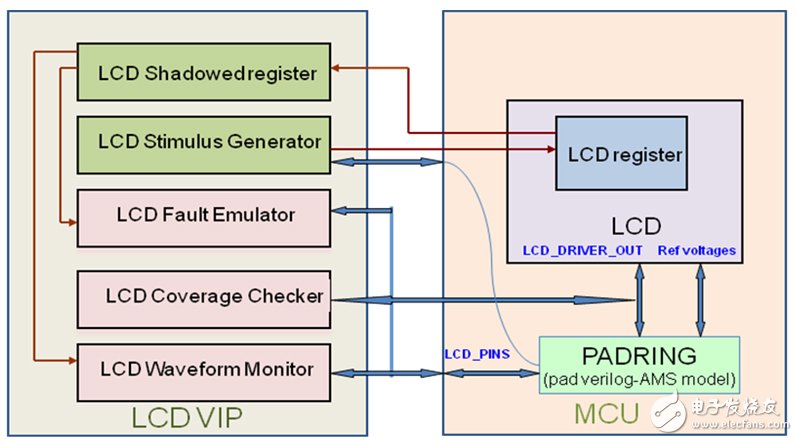

第三个挑战是验证IP。几个验证IP是分别为各个IP创建的。最复杂的混合信号VIP是分段LCD VIP,支持64个模拟LCD引脚。分段LCD的验证是采用混合信号验证方法的最佳案例。VIP包括五个部分。 LCD影子寄存器、激励发生器、波形监视器、故障仿真器和覆盖发生器。激励发生器用于产生数字和模拟激励,影子寄存器实时获得LCD内部寄存器的值,波形监视器自动检查MCU边界的LCD驱动波形,来自LCD驱动出来通过pad ring到MCU边界的设计路径也可验证。故障仿真器相关于故障检测功能。覆盖发生器协助报告模拟信号的功能覆盖,大大提高了混合信号验证的质量。

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处。

2.3.4 混合信号验证challenge4 – 功耗验证

混合信号验证的另一大挑战是功耗验证。Kinetis的功耗验证采用了CPF方法。

CPF语言提供表示设计实现和验证使用的工具所能理解的功率意图。

基于CPF的低功耗验证流程使其有能力在设计周期的早期RTL已准备就绪时验证低功耗设计意图。流程包括使用CPF进行静态检查和动态仿真。

这是Kinetis的功率域图,功率域包括padring电源域、DGO电源域、SOG电源域、VDDA电源域、RTC电源域、USB电源域、FLASH电源域、双口RAM电源域、SRAM电源域。

下面是可以通过动态CPF仿真来验证的主要项目:

·电源开关关闭(PSO)行为

·设计逻辑错误断电

·隔离规则:隔离值的正确性

·状态保持功率门控(SRPG)规则

·正确的断电供电顺序

·内存电源关闭控制

Encounter® Conformal®低功耗软件可以让你在设计过程早期使用的正规技术(相对于仿真)来验证芯片。可以用来捕获错误的功率意图规范,比如隔离单元缺失/冗余、电平转换器、或者控制信号无适当供电等,尤其是电平转换器,在动态CPF仿真中非常难以验证。也可以用来在每个验证阶段进行等效性检查。

2.3.5 混合信号验证底5大挑战 – 混合信号功能覆盖

传统上,覆盖率是用以建立信任的一个维度,对于确保验证计划完整、设计经过尽可能彻底的验证而言,这是一个安全网络。覆盖率指标是针对明示或暗示目标测量所收集的覆盖率数据,通常以百分比表示。

目前混合信号验证质量取决于混合信号验证工程师的经验。模拟信号的功能覆盖迫切需要一种通用的方法。

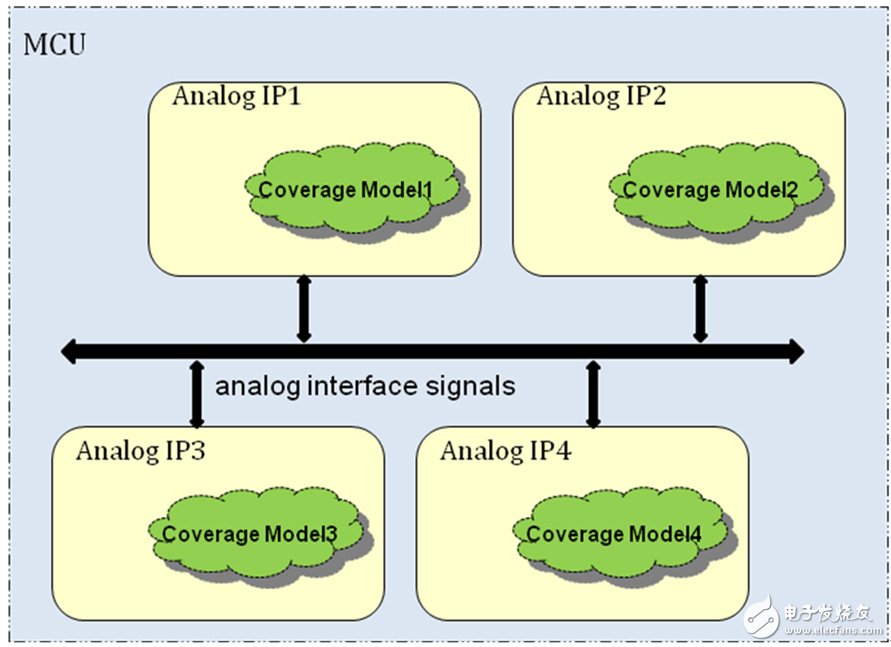

AMS designer可以支持面向控制的PSL / SVA断言,ICC也支持PSL断言和覆盖率指令。对于有几个模拟IP在内的混合信号芯片,每个模拟IP都有自己的覆盖模型。这些模型是独特的,各有不同。

这些覆盖模型是自动生成的,是模拟设计的仿真部分。

这些覆盖模型有助于产生模拟信号的功能覆盖报告,功能覆盖报告100%应该是验证流程一个强制要求,这样可以消除不完整验证可能带来的错误。

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处。

评论