浅谈嵌入式网络视频服务器的设计

嵌入式网络视频服务器是一种提供网络视频传输和共享的嵌入式设备,是为构建高可靠性的多媒体数字监控系统而设计开发的,数字监控系统是指通过软硬件将监控头采集到的图像处理成数字信号,传送到电脑进行处理。对于数字监控系统,根据系统各部分功能的不同,我们将整个数字监控系统划分为七层——表现层、控制层、处理层、传输层、执行层、支撑层、采集层。当然,由于设备集成化越来越高,对于部分系统而言,某些设备可能会同时以多个层的身份存在于系统中。控制层是整个安防监控系统的核心,它是系统科技水平的最明确体现。通常我们的控制方式有两种——模拟控制和数字控制。模拟控制是早期的控制方式,其控制台通常由控制器或者模拟控制矩阵构成,适用于小型局部安防监控系统,这种控制方式成本较低,故障率较小。但对于中大型安防监控系统而言,这种方式就显得操作复杂且无任何价格优势了,这时我们更为明智的选择应该是数字控制。

本文引用地址:https://www.eepw.com.cn/article/201710/367017.htm1 系统组成与工作原理

网络视频服务器系统又叫数字视频编码器,是一种压缩、处理音视频数据的专业网络传输设备,由音视频压缩编解码器芯片、输入输出通道、网络接口、音视频接口、RS485串行接口控制、协议接口控制、系统软件管理等构成,主要是提供视频压缩或解压功能,完成图象数据的采集或复原等,目前比较流行的基于 MPEG-4或H.264的图像数据压缩通过Internet网络传输数据以及音频数据的处理。网络视频服务器在目前视频领域中的应用主要是利用网络视频服务器构建远程监控系统。基于网络视频服务器的多通道数字传播技术具有传统的基于磁带录像机的模拟输出系统无可比拟的诸多优势,网络视频服务器采用开放式软硬件平台和标准或通用接口协议,系统扩展能力较强,能够与未来全数字、网络化、系统化、多通道资源共享等体系相衔接。

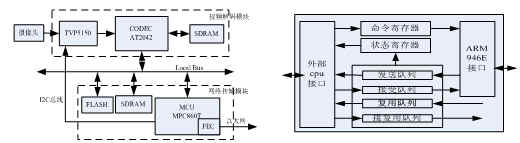

图1 系统框图 图2 AT2042与CPU的通信机制

2 视频编码模块

视频编码模块的核心是Pentamicro公司生产的AT2042,它是一个内置微控制器ARM946E 的双通道音视频编解码芯片,可支持MPEG-4/2/1和JPEG标准的视频压缩编码,具有画面缩放、颜色数据格式变换、噪声抑制滤波等功能。 AT2042能直接与IBM、Motorola、ARM、Xscale和Axis等多种CPU接口,无需其它附加电路。MPC860T对AT2042的控制和访问可通过AT2042的状态寄存器和命令寄存器以及四个输入输出队列:发送/接收队列,复用/解复用队列。AT2042与CPU的通信机制如图2所示

AT2042与CPU的通信实现情况如下:CPU通过命令寄存器来控制内置微控制器ARM946E的操作状态;通过状态寄存器来检查 AT2042内部各个FIFO的操作状态;通过接收队列给AT2042发送各种配置参数,以及所有内置微控制器ARM946E所需要的相关参数;通过复用队列将压缩编码后的比特流读出。

3网络传输模块

3.1 MPC860T最小系统设计

MPC860T是Motorola公司的高性能的32位PowerPC嵌入式处理器,有三个主要的功能模块:嵌入式的PowerPC内核、RISC通信处理模块(CPM)和系统接口单元(SIU)。MPC860有两个CPU:PowerPC和32位RISC。PowerPC执行高层代码,RISC处理实际通信的低层功能,2个处理机互相配合工作。这种双处理器构架,分担了主CPU的工作量,提高了处理效率,同时降低了芯片功耗,特别适合于各种通信及控制领域的嵌入式应用。MPC860T最小系统如图3所示。

3.1.1 电源

电源作为一个系统的能量提供者,在整个系统设计中成为必不可少且至关重要的一个环节。MPC860T的工作电压为3.3V,需提供一个3.3V/1A的直流稳压电源给CPU及外围电路。

3.1.2 时钟电路

MPC860时钟系统为所有片上或片外设备提供不同的时钟。MPC86OT一共有两个参考时钟源,一个是其工作频率的晶振,连接EXTCLK脚,一个是 32KHz的晶体,连接EXTAL和XTAL脚。设计中,两个外部时钟源都用到了。EXTCLK外接一个5MHz的晶体振荡器作为SPLL的参考时钟源,在EXTAL和XTAL之间接一个32.768KHz的晶体作为实时时钟的参考时钟源。

3.1.3 复位模块

MPC860T包括上电复位、外部硬复位、内部硬复位、JTAG 复位、外部软复位和内部软复位。复位电路采用MAX811T来实现。上电和人工按键均可产生复位信号,其中/RESET端口接MPC860T的 /PORESET,由/RESET产生复位信号复位处理器。由SN74LVTH125芯片组成的电路提供/HRESET和/SRESET复位功能。手动按下按键连接芯片/OE控制三态门的输出使能时,低电平输出到/HRESET或/SRESET,MPC860T响应复位动作。正常状态下,输出呈现高阻状态。

3.1.4 存储系统设计

MPC860T的存储控制器最多可以控制8个存储体或外围设备,支持GPCM (general purpose chip select machine)和UPM(User programmable machines)两种方式,可提供与SRAM,EPROM,FLASH,DRAM,SDRAM等设备的无缝连接。GPCM提供与 EPROM,SRAM,Flash以及其他的外设的无缝连接,UPM则常常用于SDRAM以及猝发式SRAM的控制与连接。Flash存储器是一种电可擦除、可重写的存储设备。Bootrom Flash采用512Kbyte的SST39VF040。Bootrom主要作用是引导及初始化CPU,以及引导单板程序。BSP在嵌入式系统和 Windows系统中的不同其实运行与PC机上的windows或linux系统也是有BSP的。只是PC机均采用统一的X86体系架构,这样一定操作系统的BSP相对x86架构是单一确定的,不需要做任何修改就可以很容易支持OS在x86上正常运行,所以在PC机上谈论BSP这个概念也没什么意义了。而对嵌入式系统来说情况则完全不同,目前市场上多种结构的嵌入式CPU(RISC)并存(PPC,ARM,MIPS…),为了性能的需要,外围设备也会有不同的选择和定义。一个嵌入式操作系统针对不同的CPU,会有不同的BSP,即使同一种CPU,由于外设的一点差别(如外部扩展DRAM的大小,类型改变),BSP相应的部分也不一样。

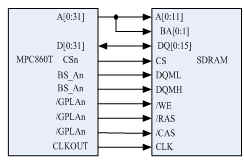

考虑存储容量、功耗等因素,数据存储器多选高速动态随机存储器SDRAM。Micron公司生产的 MT48LC4M16A2作为SDRAM芯片,组织形式为1M X 4 bank X 16位,总容量为64Mbit,采用3.3V供电,支持的最高频率为133MHz。由于其数据总线为16位,因此系统选用两片并联构成32位。SDRAM 与MPC860T的连接框图如图4所示。

图4 SDRAM与MPC860T的连接框图

SDRAM的CLK信号由MPC860T的输出时钟CLKOUT驱动,/WE、/RAS和/CAS信号分别由UPMA的GPLA1~GPLA3产生。 SDRAM的A10引脚要复用于SDRAM的刷新控制,因而必须与GPLAO相连(由于不方便连线图中未画出),因为MPC860T的GPLAO可以通过编程实现控制信号与地址信号的复用。MT48LC4M16A2内部有12条行地址和8条列地址,行地址为高位地址,列地址为低位地址,而外部仅有12条地址信号A0~A11。这就需要对UPM对地址进行复用。MPC860T支持内部地址复用,可以通过UPM的RAM字中的AMX位进行配置,同时将OR寄存器中的SAM位同时进行配置。

3.2 网络接口

经压缩的视频流由MPC860T封装成IP包后,通过网络接口送入Internet。采用MPC860T的FEC(Fast Ethernet Controller)加上物理层芯片以及脉冲变压器构造一个10/100M以太网接口,由此实现上述功能。

4 系统的软件设计

软件设计包括:VxWorks操作系统的内核生成和VxWorks下驱动程序与应用程序的开发。VxWorks是美国Wind River System公司推出的嵌入式实时开发环境,它是专门为嵌入式系统设计开发的可裁减、高性能的操作系统。为了发挥VxWorks的功能并设计出可靠、高效的嵌入式系统,还用到Tornado集成开发环境。TornadoII就是Wind River公司推出的为了开发VxWorks应用系统提供的集成开发环境,提供一种有效的方式开发嵌入式实时应用程序,同时对目标机系统的影响做到最小。

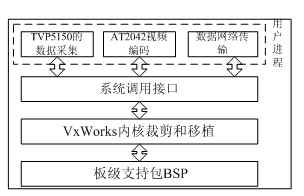

图5 软件结构框图

本系统中软件的架构如图5所示,主要包括:1)硬件底层驱动程序,包括BSP的开发、操作系统的裁剪和移植、文件系统的开发和应用等。设备驱动程序是直接控制设备操作的程序,也是设备上层的一个软件接口,功能是对I/O进行操作。只要系统访问设备就会调用驱动,从这一点可以看出,驱动程序不能自动执行,只能被系统或应用程序调用。设备驱动程序通常包含六个主要功能:对设备进行初始化、打开设备操作、关闭设备操作、从设备上接收数据并提交给系统、把数据从主机上发送给设备和对设备进行控制操作。2)应用程序的设计,它包括以下三个模块:TVP5150的数据采集、视频编码、数据的网络功能。其中 TVP5150的数据采集模块包括对TVP5150初始化,工作参数和反馈状态信息的设置等。视频解码模块除了完成对AT2042的驱动,还为上层应用提供配置管理接口。网络功能模块包括音视频编码数据的网络传输和网络服务功能等子模块。

结束语

本文作者创新点是采用MCU+CODEC的硬件结构,较其他的采用DSP单芯片的系统,具有系统集成度高,体积小、功耗低、性能稳定等优点。并且,作为MCU的MPC860T内部集成有FEC,使硬件设计更简单。同时, VxWorks嵌入式操作系统的采用使系统具有很好的实时性。

评论