利用AD7616的V型采样实现准同步数据采集

作者/ 于克泳1 叶健2 1.亚德诺半导体技术(上海)有限公司(南京 210014)2.亚德诺半导体技术(上海)有限公司(上海 201210)

本文引用地址:https://www.eepw.com.cn/article/201709/364882.htm摘要:AD7616是ADI公司推出的一款16位数据采集系统(DAS)。对于多通道非同步采样型ADC,本文采用“V型采样+数据平均”的模式在AD7616的应用中实现了准同步采样,同时基于AD7616的实验结果也验证了理论上的误差分析。

1 AD7616简介

AD7616是ADI公司推出的一款16位16通道数据采集系统(DAS) ,同一封装内集成了两个16位逐次逼近寄存器型(SAR)模数转换器(ADC),支持对16个通道进行双路同步采样。AD7616的模拟输入端为真双极性输入,每个通道的量程可独立设置,有±10 V、±5 V或±2.5 V供选择,同时输入端具有±20V的箝位(CLAMP)保护,而且片内集成有抗混叠模拟滤波器。AD7616采用+5 V单电源供电,拥有1Msps的采样速率并达到90dB的信噪比(SNR),输入阻抗与采样速率无关,恒定为1MΩ,因此无需外部的驱动电路及双极性电源。

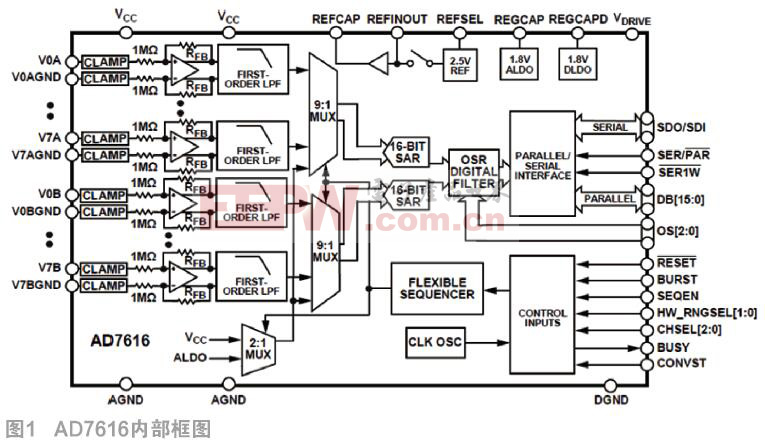

AD7616通过HW_RNGSEL[1:0]管脚进行选择,工作在硬件模式或软件模式。硬件模式下,AD7616由引脚进行配置。软件模式下,AD7616支持并口或串口对内部的寄存器及灵活的序列器(Flexible Sequencer)进行配置,以获得更多的功能。AD7616的内部框图如图1所示。

2 多通道准同步采样

电力系统保护与测控的应用中,需要实时监测电网中多相的电压和电流信号。为了满足各种标准的精度要求,传统的设计中通常都是对多路信号进行同步采样,因此一般选用多通道同步采样型的ADC,例如AD7865,AD7656-1,AD7606等都是典型的应用选择。

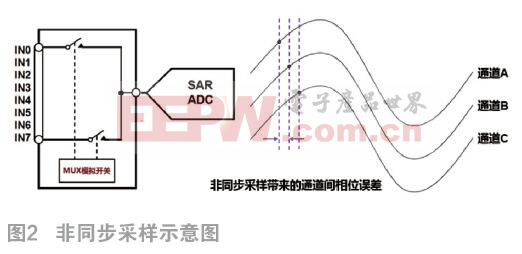

在某些需要低成本但精度要求不高的应用中,工程师尝试采用一种“MUX模拟开关+单通道ADC”的设计方案,如图2所示,利用模拟开关切换输入通道,用单通道ADC循环对输入信号进行采样。由于多通道信号的非同步采样,采样点的间隔时间会导致通道间采样的延迟,并由此带来一定的相位误差或相位失配,误差的大小与多个因素相关,取决于输入信号的频率、幅值、采样时刻信号的相位等。

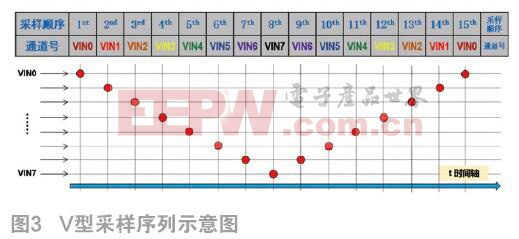

为了减少非同步采样所带来的通道间相位误差,设计一种采样序列,通道顺序为“VIN0→VIN1→ VIN2→…→VIN6→VIN7→VIN6→… →VIN2→VIN1 →VIN0”,如图3所示。由于采样序列像一个大写的字母“V”,我们不妨称之为“V型采样”模式。

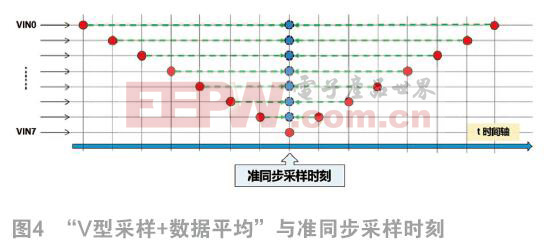

在图3“V型采样”配置下,VIN0 ~ VIN6的每个通道前后采样两次,而且采样时刻在VIN7采样时刻的两侧呈对称分布。如果ADC的采样间隔控制为等间距,当输入信号为线性信号时,VIN0 ~ VIN6通道前后两次采样数据的平均值与在VIN7采样时刻的结果是相同的,这就通过“V型采样+数据平均”的方式实现了多通道间的准同步采样,因此把VIN7的采样时间点称之为“准同步采样时刻”,如图4所示。

如果输入信号为正弦波,采用“V型采样+数据平均”的模式会带来一定的误差,但相比传统的“MUX模拟开关+单通道ADC”非同步采样模式而言,仍然可以大幅减少由于非同步采样而带来的通道间误差。

3 “V型采样+数据平均”的误差分析

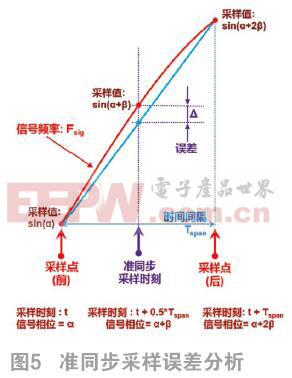

以正弦波为例,分析“V型采样+数据平均”模式得到的平均值与准同步采样时刻的采样值之间误差的大小。为了简化分析,将输入正弦波信号的幅值归一化为1.0,并假定第一个采样点时刻对应正弦波的相位为α,第二个采样点时刻对应正弦波的相位为α+2β,参考图 5所示。

1)前后两个采样点的数据平均值为:[sin(α) + sin(α+2β)] / 2 ;

2)准同步采样时刻的正弦波实际值为:sin(α+β) ;

3)“V型采样+数据平均”所带来的误差Δ为:

Δ = | [sin(α) + sin(α+2β)] / 2 - sin(α+β) | = | [1 - cos(β)] * sin(α+β) | ;

假定正弦波信号的频率为Fsig,前后两个采样点之间的间隔为Tspan,前后两个采样点的相位差:2β = 2π * Fsig * Tspan ,带入误差Δ的公式:Δ = | [1 - cos(β)] * sin(α+β) | = | [1 - cos(π * Fsig * Tspan)] * sin(α+π * Fsig * Tspan) |。

由误差Δ的表达式可以看出,一旦输入正弦波信号的频率Fsig及前后采样点的时间间隔Tspan确定后,“V型采样+数据平均”带来的误差仅与采样点时刻所对应的正弦波相位α相关,并且误差的最大值为 [1 - cos(π * Fsig * Tspan)]。

Tspan与ADC的采样率Fsample及前后采样点间的采样次数N相关,即Tspan= N * (1 / Fsample) 。按照图4的配置时,VIN0到VIN6每个通道的Tspan各不相同,其中VIN0通道的Tspan最大,误差也将会最大。假定ADC的采样率为1Msps且连续等间隔采样,则相邻两次采样的间隔为1μs,此时VIN0通道的Tspan = 14μs。以50Hz的电力系统应用为例,用Tspan = 14μs来计算“V型采样+数据平均”所带来误差的最大值:

对于50Hz (基波),误差最大值为:1 - cos(π * 50Hz * 14μs) < 0.01‰;

对于250Hz (5次谐波),误差最大值为:1 - cos(π * 250Hz * 14μs) < 0.1‰;

对于2550 kHz (51次谐波),误差最大值为:1 - cos(π * 2550Hz * 14μs) < 6.3‰;

从以上的计算结果来看,“V型采样+数据平均”的模式完全可以满足电力系统中保护和测控的精度要求。下一步将会用实验的方法进行验证。

4 AD7616准同步采样的实现

在传统的“MUX模拟开关+单通道ADC”模式中,ADC每收到一个CONVST启动转换控制信号后,仅完成一个通道的转换。这就意味着,要通过“V型采样+数据平均”的方式来实现“准同步采样”,需要处理器 (Processor) 发出一系列的CONVST启动转换控制信号来实现多个通道的采样序列,还要求处理器在每次启动转换之前读出ADC的转换数据,这既增加了处理器的负担,又降低了系统的可靠性。

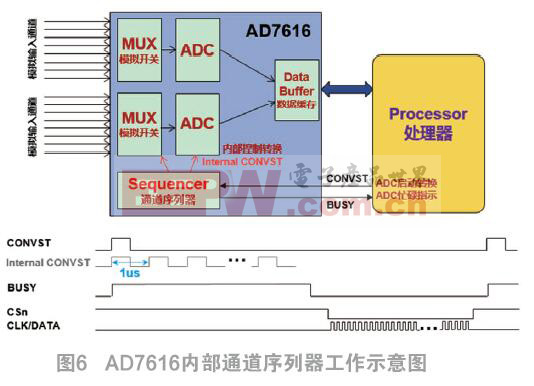

AD7616内部集成了MUX模拟开关和SAR型ADC,特别之处在于还集成有突发模式 (Burst Mode) 和灵活的通道序列器 (Flexible Sequencer) 。当AD7616工作在软件模式 (Software Mode) 下,通过设置序列栈寄存器 (Sequencer stack registers) ,处理器只需要发出一个CONVST启动转换控制信号,AD7616将会自行完成所有设置通道的转换,并把每一次的转换结果放在数据缓存区中,待全部通道转换完成后,AD7616将BUSY忙碌指示信号置低,等待处理器读取所有通道的转换结果。AD7616与处理器的连接及内部通道序列器的示意图如图6所示。

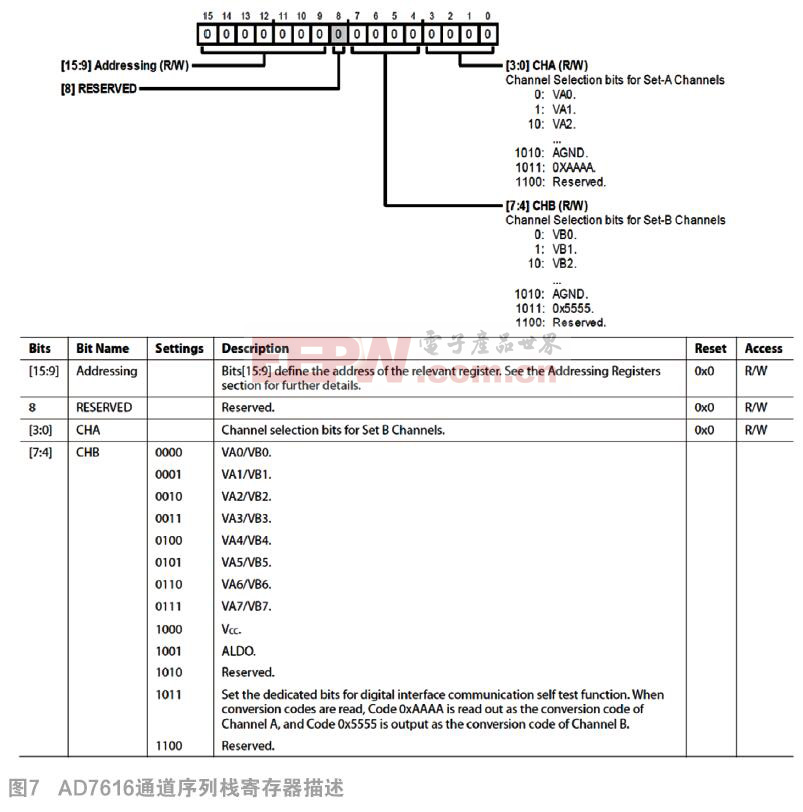

AD7616内部有两个高速ADC核,称为A核和B核。通道的序列栈寄存器地址为0x20到0x3F,总共包含32个寄存器,由用户编程来实现1到32个预定的采样序列。每个寄存器的宽度为16bit,其中 [7:4] bit定义为BSEL,用来设定B核的转换通道, [3:0] bit定义为ASEL,用来设定A核的转换通道。寄存器中的 [8] bit定义为SSREN,是通道转换序列的结束控制位,如果设定为0,AD7616将调入下一个序列寄存器的设置进行转换,如果设定为1,通道转换序列在完成本次转换后结束。转换通道的选择,除了模拟输入通道VIN0 ~ VIN7,还可以选择内部Vcc,内部LDO,或者固定输出一个标志字0x5555或0xAAAA。AD7616序列栈寄存器的描述如图7所示。

评论