基于VeriStand的制导系统半实物仿真平台的研究

作者/ 范勇 刘曌 李钊 上海航天控制技术研究所(上海 201109)

本文引用地址:https://www.eepw.com.cn/article/201708/363625.htm范勇(1987-),男,硕士,助理工程师,研究方向:实时仿真系统设计。

摘要:为保证制导系统半实物仿真的实时性和准确性,缩短开发周期,本文基于VeriStand、Simulink和PharLap组合方式构建实时仿真平台。该平台通过VeriStand实现对仿真模型的在线管理和仿真试验的控制,以及对模型参数的在线显示和修改;采用PharLap实时操作系统保证仿真模型执行的实时性,通过Simulink对系统进行建模,达到快速仿真设计、降低开发周期、弱化人为影响的目的。制导半实物仿真试验表明:仿真平台工作可靠,实时性能好,能够提高半实物仿真试验的开发效率和可靠性。

引言

运载火箭控制系统的主要功能是制导、姿态控制和指令控制等[1]。制导的任务是对火箭质心的运动参数进行实时敏感测量、计算和控制。当火箭的运动参数达到要求值时,关闭发动机,使火箭按设计的轨道飞行[1]。半实物仿真试验技术是运载火箭控制系统研制不可缺少的手段[2]。通过半实物仿真试验能够考核箭载计算机飞行软件和制导系统方案的正确性,保证火箭飞行可靠。

仿真软件是整个仿真系统的灵魂[3],仿真软件的质量直接影响半实物仿真试验结果的精度和可靠性。火箭控制系统具有高速实时的特点,在箭载计算机中,数据采样时间间隔一般为几毫秒到几十毫秒,计算周期等于采样间隔时间或它的数倍[4],这就要求仿真系统具备实时性。对于不同型号的半实物仿真,由于设计人员能力不一,不能保证仿真软件准确可靠,从而影响试验的周期和结果。

为了在线管理和控制仿真试验,保证火箭制导系统半实物仿真的实时性、可靠性,降低开发周期。本文提出一种基于VeriStand、Simulink和PharLap组合的方式构建半实物实时仿真平台,一方面通过PharLap操作系统保证了系统仿真的实时性,另一方面利用Simulink建模并生成代码达到快速仿真的目的,缩短项目开发周期。同时通过VeriStand可以实现对实时仿真平台进行管理和在线显示、修改仿真模型参数,实现对仿真过程的在线管理和控制。

1 VeriStand和平台硬件组成

1.1 VeriStand简介

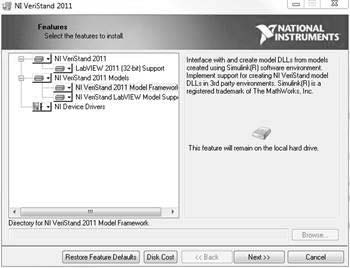

VeriStand[5]是一款开放的实时测试和仿真软件。它支持多种模型开发环境,包含Simulink、LabVIEW、MapleSim、FORTRAN/C/C++等。用户通过它能够实时编辑用户界面、控制和显示仿真模型参数、监控和管理仿真模型和实时系统。

1.2 平台硬件组成

实时仿真平台由动力学上位机和动力学实时仿真机组成。

上位机为普通PC机。

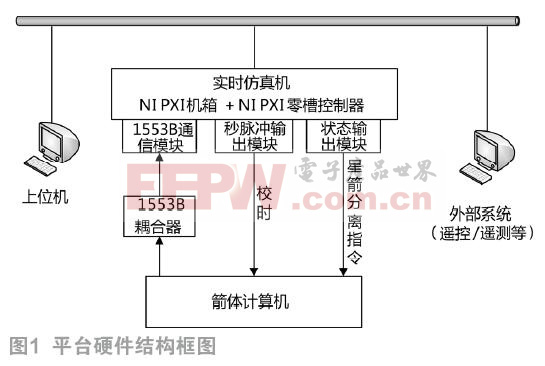

实时仿真机硬件由NI机箱PXI-1042Q、零槽控制器PXI-8110以及实现相关功能的IO板卡组成。IO功能板卡包括1553B总线通信模块、秒脉宽输出模块和状态(继电器、0/10V等)输出模块。平台硬件结构框图如图1所示。

1553B通信模块采用AIT的PXI-1553B 2通道板卡,用来模拟箭上单机的接口与箭体计算机进行1553B的数据通信。

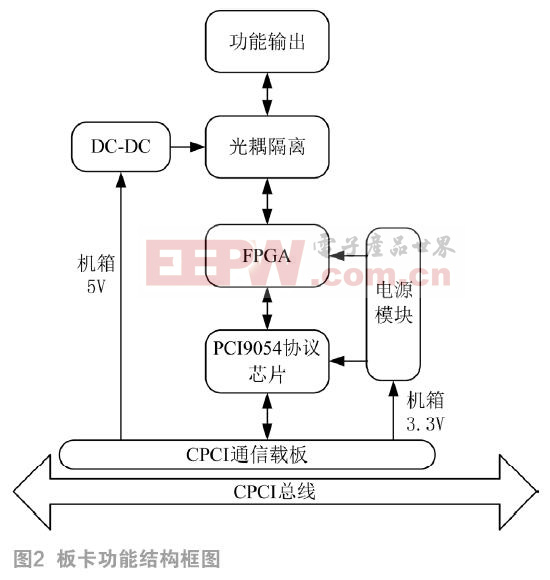

秒脉冲输出模块用来模拟GNSS秒脉冲信号,对箭体计算机进行校对;状态输出模块用来模拟星箭分离信号。秒脉冲输出模块和状态输出模块均为自研产品,结构上采用子母板结合的方式,子板的主体为FPGA,它将实现具体的逻辑功能。并将上行和下行数据进行保存。母板的主体为PCI9054,通过CPCI总线,负责FPGA的数据与零槽控制器的数据进行交换。板卡功能结构框图如图2所示。

2 仿真平台实现

2.1 实时仿真开发框架

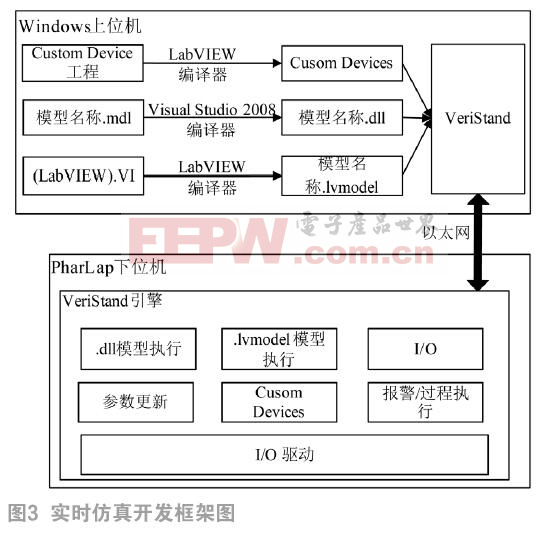

上位机为Windows系统,运行Simulink、LabVIEW、VeriStand和Visual Studio 2008四种软件环境,下位机为PharLap系统,运行VeriStand引擎,两者通过以太网连接。

在上位机完成仿真软件的设计后,通过VeriStand软件的配置和控制,将仿真软件下载到下位机中并在VeriStand引擎框架中执行;同时通过VeriStand对动力学仿真软件参数进行在线显示和修改,最终实现半实物实时仿真的目的。

实时仿真开发框架如图3所示。

2.2 平台的设计

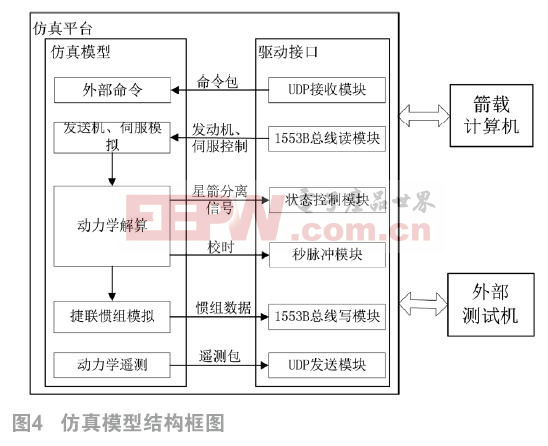

仿真平台中仿真模型由驱动接口模块和动力学仿真模型模块组成,其中驱动接口模块包含UDP接口模块、UDP发送模块、1553B总线驱动模块、状态卡驱动模块、秒脉冲卡驱动模块。仿真模型的结构框图如图4所示。

2.2.1 驱动接口设计

基于VeriStand可以采用多种方式开发驱动模块。由于Simulink工具包不包含支持PharLap实时系统的硬件驱动模块库,在仿真平台中需要根据实际使用环境来开发驱动接口模块。

1)UDP通信模块

由于UDP通信与仿真模型为串行关系,即在仿真模型一个周期开始时采集UDP接收模块的命令包,然后再在周期结束时将动力学遥测发送至UDP发送模块。因此UDP通信采用VeriStand中Custom Device的方式实现。

首先通过Custom Device模板工具生成Custom Device工程,工程中主要包含3个VI。Initialization VI完成Custom Device驱动程序被添加到VeriStand时的功能。Main Page完成Custom Device驱动程序被添加到VeriStand后配置Custom Device的功能,比如UDP通信中的IP、端口号设置等。RT Driver VI定义了Custom Device驱动被下载到下位机运行的执行行为。

2)1553B通信模块

仿真平台中1553B驱动模块分为初始化模块和读写操作模块。

通过AIT公司提供的AIT Flight Simulyzer软件能采用图形化配置的方式生成AIT 1553B板卡的初始化文件,但是只存在调用该文件的LabVIEW函数接口。因此,1553B通信初始化模块采用LabVIEW生成VeriStand *.lvmodel类型模型文件的方式实现。

在仿真模型中AIT 1553B板卡用来模拟多种箭上单机的接口,通信方式无规律,存在相应的C函数接口和LabVIEW函数接口。Custom Device的执行和仿真模型的执行是并行关系,不适合采用Custom Device实现1553B模块的读写功能。因此,对1553B模块的读写操作采用S函数[6]的方式实现。实现的功能有:1553B读数据功能、1553B写数据功能、16位CRC计算等。

3)状态输出模块和秒脉冲输出模块

状态输出模块和秒脉冲输出模块均采用PCI9054接口芯片,支持VISA[7]函数接口的调用,因此,采用S函数的方式实现。

状态输出模块和秒脉冲输出模块为自研硬件模块,在操作这些模块之前,必须使这些硬件模块能被仿真平台识别。系统中使用NI-VISA Driver Wizard工具,根据设备的基本属性(PCI Device ID和Vector ID)生成*.inf文件,然后通过FTP下传到下位机,重启下位机后PharLap实时系统就能识别该硬件基本信息并分配硬件设备名称。

状态输出模块和秒脉冲输出模块的初始化、读写操作均采用S函数的方式实现,通过VISA函数接口完成相应的功能操作。

2.2.2 动力学解算模块

该模块中通过动力学方程解算出火箭的姿态和位置信息,然后根据姿态和位置信息转换成捷联惯组的输出并通过1553B的硬件通信接口发送给箭机。

2.2.3 编译环境

仿真平台的S函数中调用了VISA库函数库和AIT 1553B驱动函数库,在VeriStand的makefile文件NIVeriStand_vc.tmf的LIBS中添加对两种函数库文件的包含,添加内容如下:

LIBS = $(LIBS) XXowl1553.lib

LIBS = $(LIBS) XXvisa32.lib

LIBS = $(LIBS)

3 仿真平台的验证

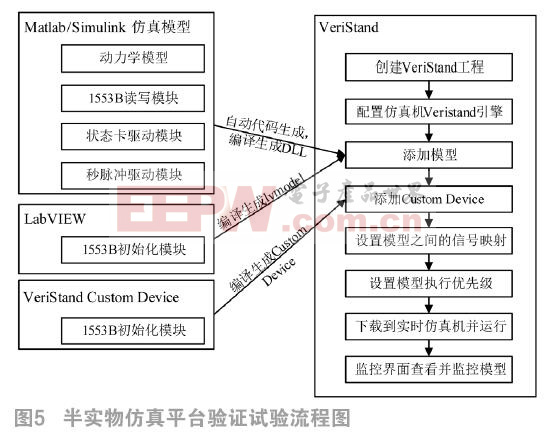

基于VeriStand 的火箭制导系统的半实物仿真平台验证试验流程如图5所示。

以某型火箭为例,该制导系统的半实物仿真平台验证试验步骤具体如下:

1)在Simulink中搭建某型火箭的仿真模型,然后使用RTW工具根据VeriStand提供的TLC文件和修改的tmf文件自动生成代码,编译生成DLL文件。

2)在AIT Flight Simulyzer软件中完成AIT板卡的配置文件的输出,通过FTP下传到下位机指定目录。通过LabVIEW编写1553B初始化程序,生成lvmodel文件。

3)通过Custom Device Template Tool生成Custom Device模块,然后添加UDP接收和UDP发送功能,最后编译生成VeriStand引擎可执行的文件。

4)将各个模块组件添加到VeriStand中,通过mapping的方式将各个组件的信号进行映射。同时,设置各个模块的执行顺序,执行顺序依次为:1553B初始化模型、UDP接收驱动、仿真模型、UDP发送驱动。

5)将配置好的VeriStand应用程序下载到下位机运行,通过VeriStand工程的监控界面实现对仿真模型参数的实时显示和在线修改。

按某型火箭搭建的制导系统半实物仿真验证平台的实物图如图6所示。该平台由动力学上位机和目标机组成。两者通过以太网连接。上位机运行Simulink、LabVIEW、VeriStand和Visual Studio 2008四种软件环境,进行火箭动力学模型及对应硬件驱动接口模型的编译、下载和硬件在环的监控管理。下位机为PharLap系统,运行VeriStand引擎,配置的IO功能板卡包括:1553B总线通信模块,秒脉宽输出模块,状态(继电器、0/10V等)输出模块。

对比某型箭机半实物仿真试验结果可知,建立的基于VeriStand的制导系统半实物仿真平台能够较快的进行箭机的硬件在环仿真,试验真实、有效,提高了半实物仿真平台实时性和开发效率。

4 结论

本文通过VeriStand、Simulink、PharLap组合的方式来构建实时仿真平台,并成功地应用于火箭制导系统半实物实时仿真系统中。试验结果证明仿真平台工作可靠,实时性能好,能够满足火箭制导系统半实物仿真的实时性要求。同时平台降低了仿真软件开发周期,增强了仿真软件设计的可靠性,实现了对仿真模型的过程监控和控制,对其它半实物仿真平台的设计有一定的参考和借鉴意义。

参考文献:

[1]顾胜,祝学军,杨华.基于1553B总线的运载火箭控制系统分析[J].导弹与航天运载技术,2005(3):9-12.

[2]陈宜成,朱友忠.运载火箭控制系统通用仿真软件设计平台[J].计算机仿真,2005(5):46-55.

[3]徐庚保,曾莲芝.勇攀世界科技高峰的中国仿真技术[J].计算机仿真,2004(4):5-9.

[4]任广辰,闫长灿.箭载计算机在运载火箭中的功能研究[J].科技创新导报,2016(20):15-16.

[5]王好端.混合动力控制器集成开发平台设计及应用[D].清华大学,2012.

[6]陈怀民,寇云林,吴成富,等.基于VxWorks半物理仿真中S-函数驱动模块的开发[J].计算机测量与控制,2009(17):599-602.

[7]鹿欣.基于LabVIEW的惯测组件实时测试系统研制[D].南京航空航天大学,2010.

本文来源于《电子产品世界》2017年第9期第65页,欢迎您写论文时引用,并注明出处。

评论