解析高速PCB设计中的布线策略

差分线对的工作原理是使接收到的信号等于两个互补并且彼此互为参考的信号之间的差值,因此可以极大地降低信号的电气噪声效应。而单端信号的工作原理是接收信号等于信号与电源或地之间的差值,因此信号或电源系统上的噪声不能被有效抵消。这就是差分信号对高速信号如此有效的原因,也是它用于快速串行总线和双倍数据率存储器的原因。

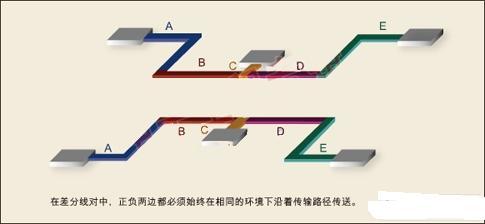

在差分线对中,正负两边都必须始终在相同的环境下沿着传输路径传送。正负两边必须紧靠在一起,以使正负信号经由这些信号上相应点的电磁场而彼此耦合。差分线对是对称的,因此它们的环境也必须对称。当然,完美的对称是不可能实现的,因为至少存在着尺寸公差。但设计师如果遵循一些基本规则还是可以获得接近理想的最佳差分信号结果。

建议

确保信号同一时间出现在每条线路的同一点上。要使走线的各段等长,如图中相同的字母表示的那样。如果差分线对带有串联端接电阻或共模滤波器,那么这些器件到差分驱动器正负两端引脚的连接距离应该是相等的。

最好按点到点布线,在任何情况下都要让分支线或支路(图中的C)保持在0.6Tr英寸以内,这里Tr指驱动器输出上升时间。图中的A和E要尽可能使用相同的长度限制规则。

采用现场解决工具(field solver)设计走线间隔,这样可以方便地获得偶模和奇模阻抗值。50欧姆的电路板并不意味着偶模、奇模或差分特征阻抗也是50欧姆。

如果为了终止某个差分信号而将它端接到地或参考电压,就应考虑应害噪声着杂环境的影响被奇模阻抗。

还应考虑端接偶模或共模(偶模值的一半)以终止有害噪声。

如果在两条线间端接,应考虑差模阻抗(奇模阻抗的两倍)。

记住,只有在差分线对紧密耦合时,来自同一个源的辐射噪声才能被有效抑制,因为只有当走线彼此靠得非常近时,周围的电磁场才可能接近相同。

延长走线长度以便补偿互补输出信号之间的任何偏移都要在靠近驱动器处进行。

尽可能只以差分方式延长走线长度,记住左右弯曲的数量和风格应该保持平衡。

图:在差分线对中,正负两边都必须始终在相同的环境下沿着传输路径传送。

避免

用单端特征阻抗代替奇模和偶模阻抗作为终端阻抗:紧密耦合的差分线对是专门针对互补信号设计的。

只是保证走线总长度相等,而不是确保走线的每一段都相等。

差分线对的布线跨越电源或地平面的间隙。

在使用自动布线工具时忘记定义差分线对,这样只能得到单端布线。

让测试工程师在差分线对每一边的不同位置增加测试焊盘。测试焊盘相当于高阻抗器件的输入,因此很容易使差分线对失去平衡。

其它信号的布线过于平行地接近差分线对,或正好在下面或上面的另一层上,它们产生的串扰可能让差分信号失去平衡。

在不相关的电源或地平面(例如单独的模拟电源平面)的上面或下面布线差分线对。

忘了考虑板外连接去向。在利用仿真检查目标电路时,系统中其它板上的连接器、电缆和差分拓扑都应被建模。

被探针或测试设备的寄生电感和电容所蒙蔽。如果在差分线对的一边放置一个探针,很可能会致使差分线对失去平衡,这时的测量很容易被误导,设备也很可能在这种测试情况下出现假故障。

评论