基于DSP的谐波测量系统

0 引言

本文引用地址:https://www.eepw.com.cn/article/201706/347792.htm随着电力电子技术的发展,越来越多的非线性器件应用到电网中,给电网带来了严重的谐波污染,致使供电电压波形畸变。目前,电力系统谐波污染与功率因数降低、电磁干扰已并列为电力系统的三大公害。谐波的危害不仅影响供电质量,而且对用电设备也会造成严重的损耗,如增加设备的温升,使绝缘部分老化,影响设备的工作质量,缩短设备寿命,并且会影响电能计量装置的准确性。谐波污染使线性用户产生不必要的费用,而非线性用户作为谐波污染源,反而会少计量电能,这是极其不公平的[1]。因此,对电网中的谐波进行准确的测量,以此来对谐波源进行治理,是提高当今供电质量的重要措施。为此,本文以高精度的数字信号处理芯片TMS320VC5409[2]为系统核心,设计了关于谐波的实时测量与计算装置,用来对电网信号进行实时采样、谐波分析和计算结果显示。

1 硬件结构和功能

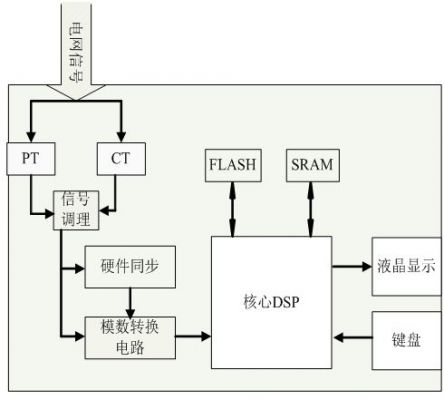

本系统主要是由核心DSP、模数转换电路、液晶显示电路以及键盘电路组成。电网信号经过电压互感器和电流互感器后,由信号调理电路变为模数转换电路能够处理的信号,然后送入模数转换电路,将模拟信号变为离散的数字信号,采样到的数据经过DSP芯片的分析计算后送入到液晶电路,对计算后的数据进行显示,以供查看。键盘主要用来控制液晶对数据的显示,控制液晶进行翻页等功能,系统框图如下:

图1 系统的总体框图

1.1 采样同步及A/D转换

电网系统中的电流和电压是含有多次谐波且基频不稳定的信号,当采样信号的频率和被采样信号的频率不同步时就会产生频谱泄露,影响谐波测量的准确性。在谐波测量的测量过程中,采用何种方法对信号进行准确的采样是关键的一步,交流信号的采样方法包括:同步采样法、准同步采样法和非整周期采样法。本文采用同步采样法,为了达到同步采样的目的,对每周期的信号采样同样的点数,本文利用锁相倍频电路来产生同步采样脉冲信号,电路是由锁相环芯片74VCH4046和CPLD构成的,被测信号经过一个方波电路,变成所需要的方波信号,然后由锁相环芯片和CPLD对信号进行同步和512倍频,从而在被采样的信号的一个周期内产生512个采样脉冲信号,控制模数转换电路对信号进行采样和A/D转换。74VHC4046能使输出信号的相位随着输入信号的相位做出改变,最终达到信号的同步。所以这个锁相倍频电路不需要软件的干预,节省了软件资源;又因为此电路所有功能均由硬件完成,还提升了检测的速度。

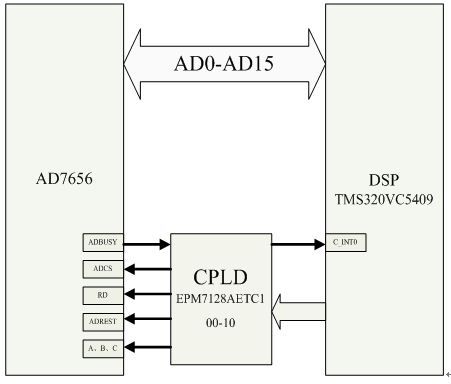

本设计采用 ADI 公司的高速高精度模数转换芯片 AD7656,其内部拥有6个单独的16位ADC,可以实现6路同步采样。最高采样速率可达250kS/S,双极性模拟输入,片上具有电压参考源和参考缓冲,也可以由外部引入参考源,转换后数据有串行和并行传输方式。AD7656和DSP的连接方如下:

图2 AD7656和DSP的连接图

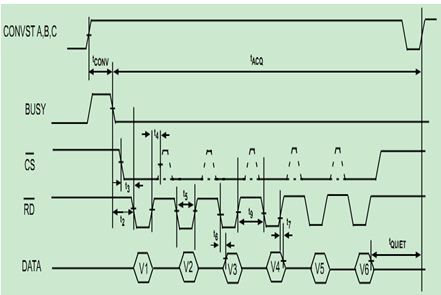

在本系统中AD7656与DSP采用并行数据传输方式,将CONVSTA、CONVSTB、CONVSTC并在一起,以启动6路AD同时采样,启动信号由采样信号控制,不需要DSP的干预。AD7656的片选信号ADCS、读信号RD、复位信号ADRST由DSP通过CPLD来产生控制逻辑,下图为AD7656的并行读时序图:

图3 AD7656并行读时序图

在并行模式下,当ADBUSY信号变低时说明转换结束,ADBUSY信号连接到DSP的外部中断0,以中断的方式通知DSP对转换后的数据进行读取。此时将/CS和/RD都置低使能输出总线,转换后的数据被输出到并行数据总线上,DSP就可以依次进行6路输出信号的读操作。

1.2 DSP核心电路

本系统的处理核心采用TI公司的TMS320VC5409,它是16位的定点DSP,除了DSP通用的结构特点以外,它还具有:16K×16的片上ROM,32K×16位的片上双寻址RAM,拥有丰富的片上外设:软件可编程等待周期发生器(SWWSR)和可编程分区转换逻辑电路(BSCR),片上锁相环时钟发生器,3个多通道缓冲串行口(McBSP),增强的8位并行主机接口(HPI),6通道的DMA控制器,本芯片也可在低功耗情况下工作。

此DSP的核心电压是1.8V,I/O电压是3.3V,而其他的器件大多是5V的驱动电压,所以本系统选用ALTERA公司的CPLD——EPM7128AETC100-10进行电平转换和逻辑控制,主要用来DSP与其他芯片之间的通信与地址译码。因为在本系统中需要对采样的数据进行大量的运算,产生的数据再加上运行的程序使DSP的片上存储资源捉襟见肘,所以为DSP外扩了FLASH和RAM存储器[3]。

1.3 液晶显示电路

本设计采用的是LCM128645ZK液晶进行显示,本液晶模块的液晶屏幕为128*64,可显示4行,每行可显示8个汉字。与DSP可以进行并行8位/4位和串行3线/2线的连接方式。中文液晶显示模块可实现汉字、ASCII码、点阵图形的同屏显示,广泛的应用于各种仪器仪表、家用电器和信心产品上作为显示器件。本系统中液晶与DSP之间采用串行数据传输方式,液晶的第15引脚(并行/串行传输方式选择引脚)接地时,液晶为串行工作模式。此时液晶的第5引脚为串行数据线,第6引脚为串行输入脉冲。DSP通过这2 个引脚即可在液晶上显示出数据或波形。液晶的6脚与DSP串口2的缓冲串行口数据发送端BDX2引脚相连,作为时钟信号,5脚与串口2的帧同步脉冲输出端BFSX 2引脚相连,DSP串口的这俩根引脚被设置为通用输入输出引脚GPIO。当DSP将数据处理完后通过这俩根引脚将计算后的数据送到液晶进行显示。下图是本液晶的串行传输时序图:

图4 液晶串行传输时序图

当片选信号CS为高电平时,同步时钟线(SCLK)上输入的信号才会被接收,另一方面,当片选信号(CS)为低电平时,模块内部的串行传输计数与串行资料将会被重置,也就是说在此状态下,传输中的资料将被终止清除,并且将待传输的串行资料计数重设回第一位,因此,模块选择引脚(CS)可被固定接到高电平。

模块的同步时钟线(SCLK)具有独立的操作,但是当有连续多个指令需要被传输时,必须确实等到一个指令完全执行完成后才能传送下一笔资料,因为模块内部没有传送/接收缓冲区。

2. 系统的软件设计

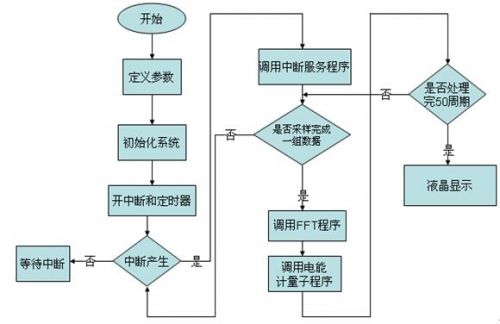

本系统的软件主要是完成对信号的采样、对采样数据的FFT变换[4]、对变换后的数据进行谐波的各项参数(谐波的幅值、有功功率、视在功率、功率因数、谐波含量)等的计算以及对计算后的数据进行显示等。软件流程图如下:

图5 软件流程图

因为本系统使用的是定点DSP,而采样数据经过FFT运算以后产生的数据为浮点数,直接进行浮点数运算不能满足系统的实时性要求,通过TI自带函数库中关于FFT函数的调用,可以达到系统对实时性的要求。

3、设计结果测试与分析

最后利用达盛科技的NC-2100综合设计试验台对本系统进行了测试,该实验台可以输出俩路信号并进行混频,一路输出50HZ的基波信号,另一路依次输出150、250、350、450、550HZ的信号,既3、5、7、9、11次谐波,两路信号进行混频后输入到系统,分别进行1%和10%谐波含量的测试,测试结果如下:

表1 各相依次加1%的各次谐波的测试结果

表2 各相依次加10%的各次谐波的测试结果

4、结束语

本系统以数据处理能力强大的16位定点DSP芯片TMS320VC5409为数据的处理核心,充分的利用了DSP强大的数据处理能力,对采样到的数据进行了FFT变换和谐波分析,且改系统的精度较高。

评论