2.5 Gbps收发器中相位锁定检测电路的设计与仿真

摘要:相位锁定检测电路是锁相环环路的关键电路,其性能的优劣直接影响了整个系统的工作。本文描述了相位锁定检测电路的工作原理,根据项目实际提出一种相位锁定检测方案,按照全定制设计流程采用SMIC0.18μm CMOS混合信号工艺完成了电路的设计、仿真。结果表明该电路在2.5Gbps收发器电路中可以稳定可靠地工作。

本文引用地址:https://www.eepw.com.cn/article/201610/309036.htm锁相环是高速多通道串行收发系统中的关键电路,相位是否准确对齐对于系统性能有着重要影响。电荷泵锁相环因其稳定性高,捕获范围大,便于集成等特点而别广泛应用于无线通信、频率综合器和时钟恢复电路中,为保证系统性能,锁相环通常都集成了相位锁定检测电路。

相位锁定检测电路通常包括模拟锁定检测和数字锁定检测两种方法,模拟检测方法采用经鉴频鉴相器PFD输出的相位误差,产生脉冲信号对外部电容进行充电和放电,以指示当前相位是否锁定,精度往往较低;数字锁定检测方法具有可编程性且设计易于实现等优点,但相位误差参数受锁相环工作环境的影响较大,可能导致相位误差超出锁相环的最大锁定窗口。

本文根据2.5 Gbps高速串行收发器的工作实际,设计了双环时钟数据恢复电路中锁相环路的相位检测电路,该电路模拟和数字方法,采用全定制的数字设计,电路工作精度高,可以达到时钟周期的1/218,能够满足G比特级数据收发的性能要求。电路采用SMIC 0.18μm CMOS工艺实现并基于spectre进行仿真,结果显示电路可以正常工作,符合预期要求。

1 锁定检测电路的结构

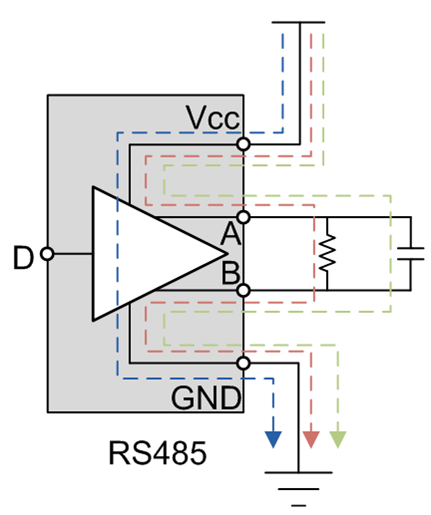

电荷泵结构的锁相环南鉴频鉴相器(PFD)、电荷泵(CP)、低通滤波器(LPF)、压控振荡器(VCO)和分频电路组成。鉴频鉴相器比较输入参考时钟和反馈时钟的频率、相位误差,当反馈时钟落后于参考时钟(即正相差)时,产生UP信号;当反馈时钟超前于参考时钟时(即负相差)产生DOWN信号。电荷泵连接PFD和滤波器LPF,它实际是一个电压/电流转换器,将PFD输出的误差电压电压转换成电流对低通滤波器进行充电、放电,通过低通滤波器转换为压控振荡器的控制电压的升高或降低,从而调整压控振荡器输出时钟相位累积的快慢,分频电路将VCO的输出时钟进行分频后送给PFD,与外部参考时钟进行比较,以输出频率、相位误差脉冲,锁定检测电路用于时钟的相位对齐检测,保证输入到时钟数据恢复环路的时钟的稳定。

在本文设计电路所应用的环境中,锁相环输入的外部参考时钟频率为125 MHz,而分频器的分频比为20,那么VCO的输出时钟频率为2.5 GHz,但由PLL环路送给收发器中时钟数据恢复电路的是1.25 GHz的时钟,因此应将VCO的输出信号经过一个二分频及相位调整电路后才可以送给收发器供时钟数据恢复电路使用。

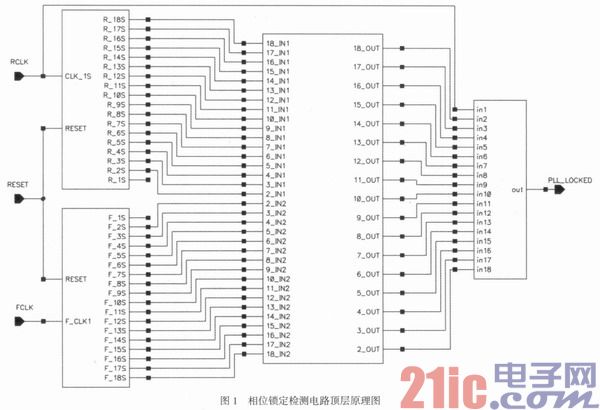

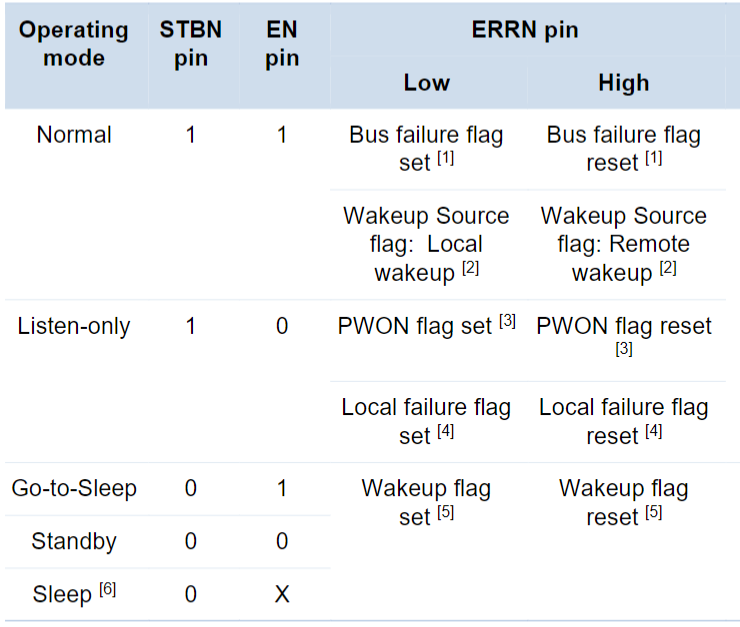

本文设计的相位锁定检测电路结构如图1所示。该电路主要包括两个可实现218分频的分频电路、18组两输入异或门构成的相位比较电路、一个18输入或非门构成锁定检测电路。输入参考时钟和反馈时钟分别进行18级分频,各级分频信号对应异或,其异或结果送给18输入的或非门。当各级分频时钟对应相同时,则异或门输出为0,此时经时序输出PLL_LOCKED信号为低电平表示锁定。

1)18级分频电路

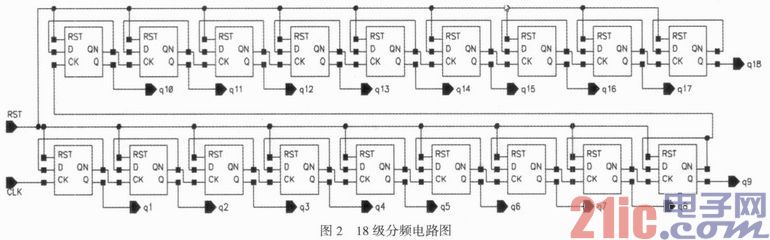

由于将D触发器的输出端取反后连接到输入端,则输出信号即为时钟信号的2分频。因此要对时钟进行218分频,则只需由将18个D触发器依次级联即可,电路如图2所示。每个D触发器采用主锁存器为负锁存器、从锁存器为正锁存器的主从结构,上升沿触发,带有异步复位,经过仔细地参数设计,触发器工作频率可以达到2.5 GHz以上,满足电路的工作速度要求。

2)相位比较电路

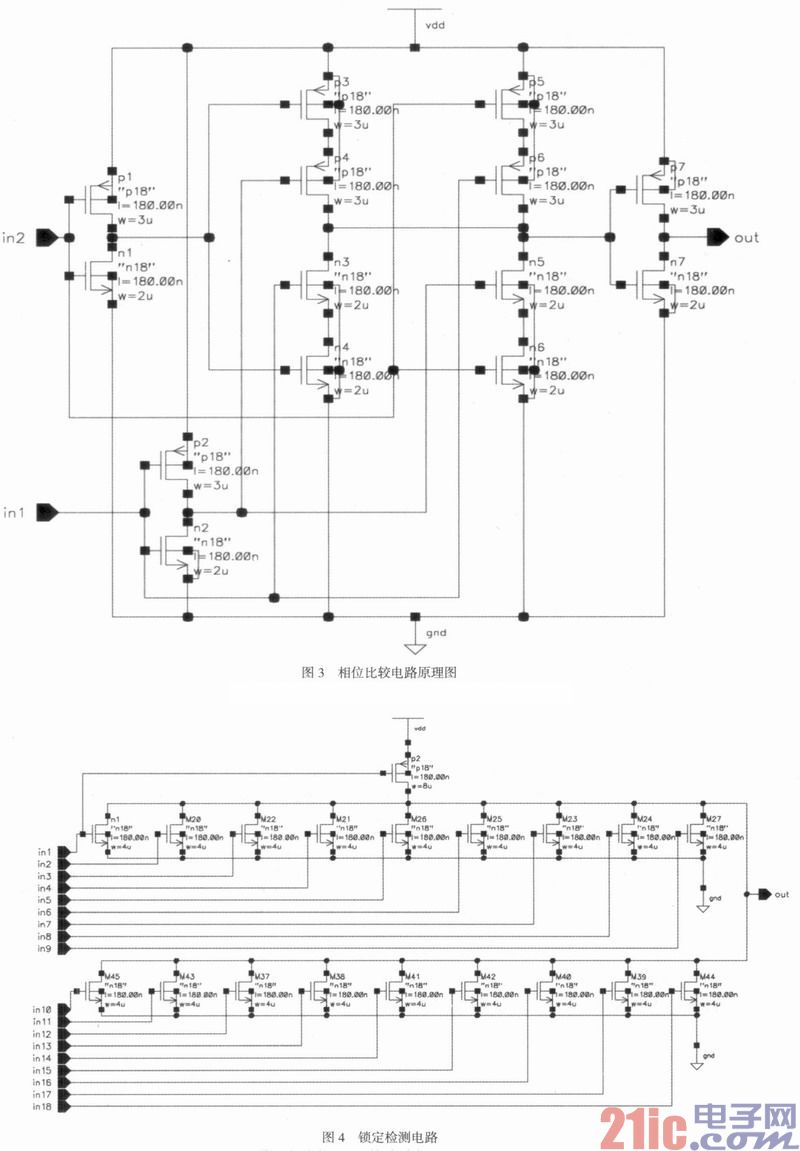

相位比较电路由18组独立的两输入异或门构成,每个异或门用于比较锁相环的参考时钟的18个分频输出与由压控振荡器产生并经20分频后得到的时钟的18个分频结果,达到在时钟周期的1/18精度上的相位对齐。为了保证电路工作的时序要求,异或门的参数也经过仔细设计与调试,可以满足性能要求。异或门电路如图3所示。

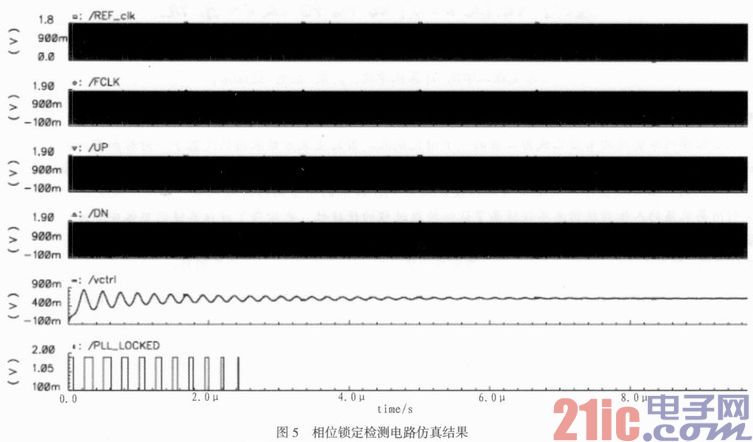

3)锁定检测电路

锁定检测电路由一个18输入的准NMOS或非电路构成,在设计时可以增加一点考虑:这里的或非门是18输入,而且若时钟的第一级分频结果就不相同,则之后各级均不相同。因此可将第一级分频结果同时作为或非门的偏置信号,可以起到低功耗控制的作用。电路如图4所示。

2 电路仿真

为验证电路的功能性能是否符合要求,采用smic0.18μmCMOS工艺完成电路设计后,在cadence的spectre上进行仿真,仿真结果如图5所示。从图中可以看出当输入时钟和反馈时钟同相以后,需要等待218个时钟周期后会输出有效锁定信号,整体闭环仿真中控制电压逐渐稳定,锁相环进入动态平衡。

3 结论

文中描述了锁相环的关键电路,相位锁定检测电路的设计与仿真,通过分析常用的相位锁定检测方法,根据设计实际提出了一种全定制的数字实现方案,可以实现1/18时钟周期的精度检测,保证了电路的可靠稳定工作,采用SMIC0.18μm CMOS混合信号工艺完成了电路的设计、仿真,结果表明该电路在2.5 Gbps时钟数据恢复电路中可以稳定可靠地工作。

评论