基于SM61580的MIL-STD-1553B总线终端设计

摘要:通过对MIL-STD-1553B总线的研究,实现远程终端(RT)与总线控制器(BC)之间高效、可靠的数据通信,提出了一种基于SM61580的MIL-STD-1553B总线终端设计方案。选用SM61580芯片,利用SM7C133存储功能,并结合MSP430F247的控制优势,采用透明模式连接芯片与处理器,实现1553B总线终端设计。该1553B总线终端系统的应用具有普遍的实用性。

关键词:1553B总线;SM61580;MSP430F247;终端

MIL-STD-1553总线是美国国防部制定的一种具有可确定性且传输可靠的数据总线,被广泛应用于军用飞机、军用车辆以及舰载等领域中。1553B终端系统可以使用8位单片机,16位单片机,32位单片机来实现。本设计选用SM61580接口芯片,设计了基于MSP430F247单片机的硬件接口电路,完成了软件接口程序,最终实现了1553B终端(RT)与总线控制器(BC)之间高效、可靠的数据通信。

1 MIL-STD-1553B总线

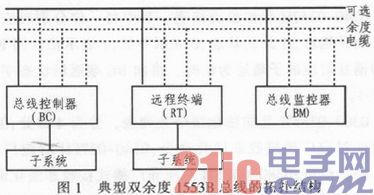

1553B总线网络由终端、子系统和总线传输介质组成,结构如图1所示。终端是使数据总线与子系统相连接的电子组件。子系统为从多路数据总线上接收数据传输服务的装置或功能单元。总线控制器(BC)是总线系统组织信息传输的终端。总线监控器(BM)是总线系统中指定做接收且记录总线上传输的信息并有选择地提取信息以备后用的终端。远程终端(RT)是总线系统中不作为总线控制器或总线监控器的所有终端。

1553B总线的传输速度是1Mb/s,采用曼切斯特Ⅱ编码,半双工工作方式。1553B总线有10种消息格式,每个消息至少包含两个字,每个字包含有16个信息位、一个奇偶校验位和3个位长的同步头。适用于变压器耦合的曼切斯特II编码,通过双绞线可靠传输的长度可以超过30 m。

2 SM61580芯片的功能特点

SM61580为微处理器和1553B总线之间提供了完整、灵活的接口电路。

SM61580芯片包含两个低功耗收发器和一个全双工译码/编码器,一个完整的BC/RT/MT(总线控制/远程终端/监视模式)多协议逻辑电路,存储器管理电路和中断逻辑电路,4Kx16bit共享静态RAM,以及一个灵活的缓冲接口与主处理总线相连。

SM61580的内部地址锁存器和双向数据缓冲器,可直接与主处理器总线相连,支持16位和8位的微处理器,并可与处理器共享一个缓冲RAM。

SM61580还可通过DMA接口电路与一个16位处理总线相连。

SM61580有3种监控模式:字监控(word monitor),选择信息监控(selective message monitor),远程终端与选择监控组合(combined RT/selective monitor)。

3 SM61580内部RAM资源分配

SM61580内部具有4Kx16共享RAM。在RT增强模式中,两个堆栈指针分配在固定的位置:0100H是堆栈指针A的地址;0104H是堆栈指针B的地址。0000-00FFH是256字的堆栈A空间,也是1553B接收信息描述符区,每个描述符占4个字,一共可储存64个描述符。描述符的4个字分别是块状态字、时间戳,接收数据块指针、接收命令字。

0108-010FH是模式命令选择中断表,设置每一个接收、发送、广播接收、广播发送的模式命令时,是否产生中断。

0110-013FH是模式命令返回数据的固定地址,当RT接收到一个模式命令时,将储存于对应位置的数据自动返回给BC。

0140-01BFH和01C0-023FH分别是RT的A/B区域地址查询表。对于A区域,地址分为4部分:0140-015FH分别对应子地址0到子地址31的接收数据缓冲区的首地址;0160-017FH分别对应子地址0到子地址31的发送数据缓冲区的首地址;0180-019FH分别对应子地址0到子地址31广播模式数据缓冲区的首地址;01A0一01BFH分别对应子地址0到子地址31的子地址控制字,可以设置数据缓存区的大小和工作方式,如:单消息模式、双缓冲模式和循环缓冲模式。

0240-0247H是忙位查询表,其中每一位分别对应子地址0到子地址31的忙状态,0表示不忙,1表示忙。当RT收到的消息对应的子地址为忙时,将向BC端返回状态字的忙位置1。

0300-03FFH是非法化指令查询表,分为4部分:0300-033FH对应广播接收非法化命令;0340-037FH对应广播发送非法化命令;0380-03BFH对应非广播式接收非法化命令;03C0-03FFH对应非广播式发送非法化命令。当RT收到非法化命令字时,将向BC返回对应的状态字。

0260-02FFH和0400-0FFFH为数据缓存区。这部分空间可以由子地址0到子地址31的子地址控制字设置每个子地址对应的数据缓存区空间的大小和工作方式。

4 SM61580与MSP430F247的接口设计

4.1 硬件接口设计

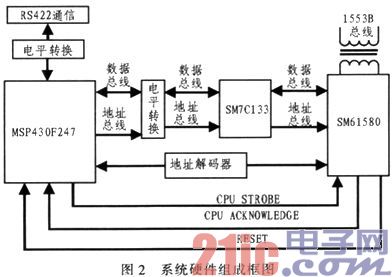

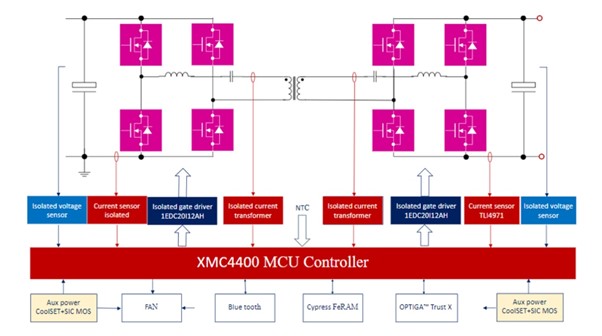

SM61580与16位处理器的连接方式采用16位透明模式。透明模式使用外部双端RAM,这使得主处理器能迅速的访问RAM(只受到RAM的速度限制);在这种模式下,可消除SM61580的调整延时。系统框图如图2所示。

在双端RAM的接口,RAM的一端由主CPU访问,另外一端可为SM61580通过存储器的控制信号,由1553B逻辑电路访问。地址和数据总线需要三态缓冲器来为CPU访问SM61580的内部寄存器。SM61580输入信号MEN/REG直接与逻辑0信号相连,SELECT与地址解码器输出1553REGSELECT相连,从而进行寄存器访问操作。

引脚RTAD4-0和RTADP通过跳线可以选择SM61580的地址编号。芯片采用外部接16 MHz晶振工作方式。

其中双端RAM采用的是SM7C133。

SM7C133是一款高速CMOS双端口静态RAM,容量为2Kx16bit。

SM7C133有两组独立的端口、地址、I/O管脚,并且在进行读或写操作时异步访问存储器。CE是自动低功耗的控制端,允许对应端的片内电路进入待机功耗模式。

SM7C133有2组独立的端口,包括地址线、I/O线,控制线,可以单独访问存储器进行读写操作。SM7C133中CE是自动低功耗的控制端,当没有选择(CE=1)时,各端口进入待机模式。当某端口的CE使能时,可以访问整个存储阵列。

为了保证写操作有效,数据必须在WR/的上升延之前建立并持续。写操作由SDtWR/管脚和CE管脚控制。2个WR/管脚用来分别控制IO口的高字节与低字节。

如果一个端口写数据到一个地址,而另一个端口试图去读这个地址,数据必须经过一个端口到端口的流通延时,才可以在输出端口被读出,否则,读出的数据是不确定的。

微控制器选用MSP430F247单片机,其特点如下:强大的处理能力;超低功耗;系统工作稳定;丰富的片上外围模块。

为了在开发过程中验证1553B总线终端传输数据的正确性,终端上制作了RS422接口,便于计算机显示总线上的收、发数据。

4.2 软件接口设计

SM61580内部具有25个寄存器,包括17个通用控制寄存器和8个测试寄存器。其中,设置17个通用控制寄存器是软件接口设计的关键。

设置启动/复位寄存器,先进入复位状态;设置配置寄存器3,进入增强模式;设置中断屏蔽寄存器,使能消息结束中断;设置配置寄存器2,进入增强型RT存储器管理模式;设置配置寄存器3,增强模式允许。设置配置寄存器1,进入RT工作方式,开启RT。

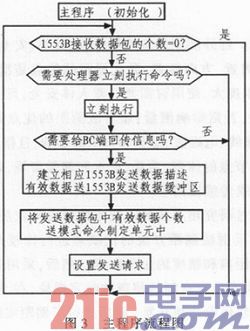

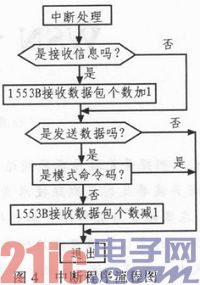

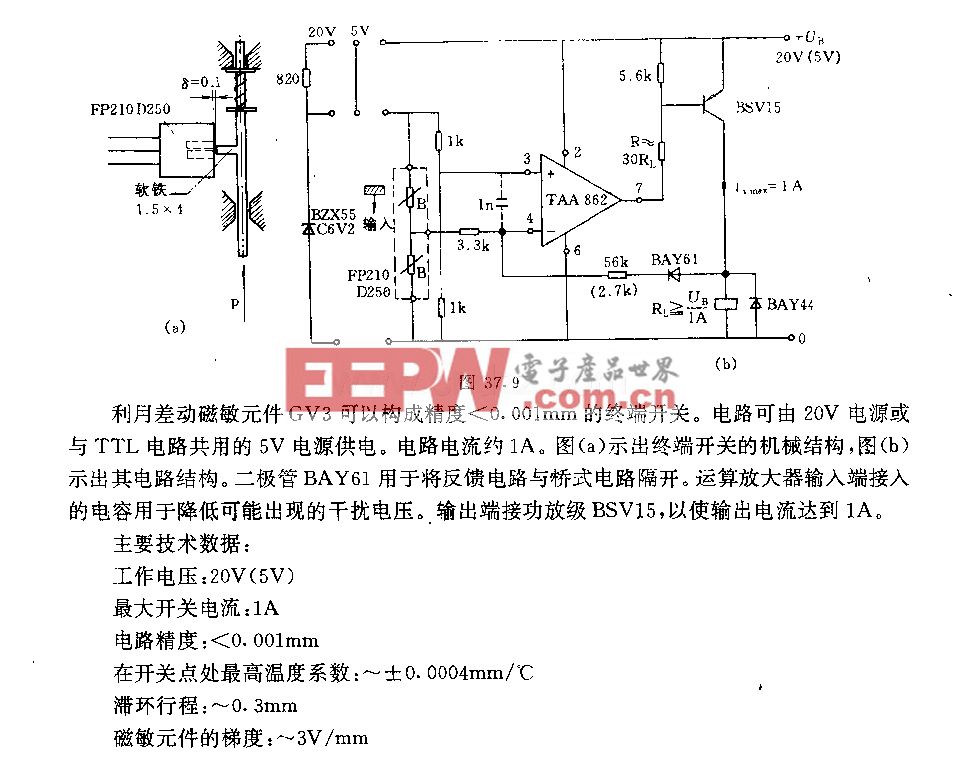

主程序对1553B信息的处理采用中断处理方式。从BC端发送来的1553B命令有2种要求:不需要RT回传数据和需要RT回传数据。

1)不需要RT回传数据

BC端发送命令字为非模式命令,要求RT接收信息,单片机终端收到信息进入中断程序,设置相应的任务标志,然后进入主程序,根据155 3B接收信息描述符区中接收数据块指针,找到1553B接收数据缓冲区,然后执行这些数据对应的任务,然后在主程序循环等待下一次中断。

2)需要RT回传数据

首先BC端发送命令字为非模式命令,要求RT接收信息,单片机终端收到信息进入中断程序设置任务标志,然后进入主程序,找到1553B接收数据缓冲区,执行相关任务,并把需要返回给BC端的数据准备好,保存在1553B发送数据缓冲区,且将需要回传数据字个数保存到模式命令对应的地址单元,然后设置服务请求,将配置寄存器1中的第9位设为0。与此同时,BC端向RT一直发送空指令,得到相应的返回状态字,判断状态字的第11位,若为1,表示RT将数据准备好,BC向RT发送模式命令,命令编码为10000,即为发送向量字命令,要求RT发送消息。RT收到模式命令后,返回状态字,且将准备好的数据个数返回给BC;然后BC端再发送一次非模式命令,要求RT发送消息,数据个数为刚才收到的返回值。此时,BC端再次收到返回的状态值和RT回传的有效数据。基于SM61580的单片机终端系统程序流程图如图3、图4所示。

5 结论

文中重点介绍了SM65180接口芯片的功能特点和RAM资源。并且给出了基于SM61580的MIL-STD-1553B单片机终端系统的硬件和软件设计方法。在多次的系统调试试验中,RT终端系统与BC总线控制器之间实现了高效、可靠的数据通信。该1553B总线终端系统的应用具有普遍的实用性。

评论