基于DM642的嵌入式网络视频服务器的设计

引言

本文引用地址:https://www.eepw.com.cn/article/201609/303349.htm目前的安防监控领域的主流产品是DVR(数字硬盘录像机),它的主要特点是适合监控点集中的局域监控应用。但是,随着对于远程分布式监控需求的增长,嵌入式网络视频服务器以其可靠性高,组网方便等优点越来越受到安防领域厂商和客户的重视。视频服务器的解决方案有多种选择,但是市场产品的主流一般选择两种方案:(1)CPU+ASIC。该方案选择以ARM为核的CPU和专用媒体处理芯片搭建。优点是开发时间相对较短,但由于采用ASIC,灵活性较差,产品一旦定型,很难更改。(2)采用面向媒体处理的专用DSP。其开发时间不长,优点是由于算法是软件代码,所以可以不断对产品性能进行升级,重复开发成本较低。基于以上几点,本系统采用第二种方案设计。

一.系统的硬件设计。

视频服务器最主要的功能是完成图像和声音的采集、压缩及传输的功能。视频服务器用到的核心技术一般包括视频压缩算法,音频压缩算法,网络传输协议。目前市场上的主流技术主要是MPEG4或H26x视频压缩算法、AAC音频压缩算法、G.72x语音压缩算法(或AAC音频压缩算法),TCP/IP协议等。DM642是TI公司推出的一款针对多媒体处理领域应用的DSP,它是在C64x的基础上,增加了很多外围设备和接口。该DSP为548脚BGA封装,高度集成化。主要外围设备包括:三个可配置的视频接口,可以和视频输入,输出或传输流输入无缝连接。VCXO内插控制端口(VIC)10/100Mbps以太网口(EMAC)。数据管理输入输出模块(MDI0)。多通道音频串行端口(McASP)。I2C总线模块。两个多通道有缓存的串口(McBSPs)。三个32-bit通用定时器。用户可配置的16-bit或32-bit的主端口接口(HPI16/HPI32)。 6Mhz32-bit的PCI接口。通用I/0端口((GPIO)。64-bit的外部存储单元接口,支持和同步或异步存储单元的连接。

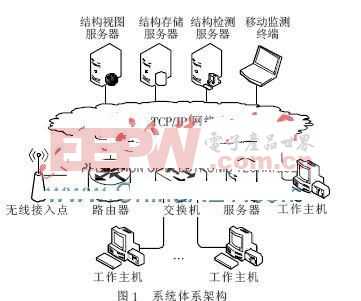

系统硬件框图如下:

本系统设计3路视频端口,2路板上解码器和1路板上编码器,32Mbytes同步DRAM 通过FPGA的OSD 4Mbytes Flash memory ,10/100以太网端口通过FPGA内寄存器执行的板卡软件配置导入加载选项配置。DSP芯片通过64bit的EMIF接口或8 /16bit的3路视频接口连接板上外围设备。SDRAM、Flash、FPGA和UART每一个设备占用其中的一个接口。EMIF接口也连接扩展背板接口,扩展背板接口用来连接背板。 板上的视频解码器和编码器连接到视频端口和扩展连接器上。母板上的2个编码器和1个解码器都符合标准规范。McASP可以通过软件重新设定成为一个扩展接口。可编程逻辑门阵列又被称为FPGA,用来执行板上组合在一起的逻辑程序。FPGA有基于软件用户端口的寄存器,用户可以通过读写这个寄存器来配置板卡。

系统的硬件设计主要有以下几个部分。

(1)存储器映射。C64xx系列DSP有大量的字节可设定的地址空间。程序代码和数据可被存储在统一标准的32bit地址空间的任何位置。 默认状态下,内部的寄存器从0x00000000地址空间开始存储。一小部分存储器可由软件重新映射为L2高速缓存,而不是固定的RAM。 EMIF(外部寄存器端口)有4个独立的可设定地址的区域,称为芯片使能空间(CE0-CE3)。当Flash、UART和FPGA映射到CE1 时,SDRAM占据CE0。背板使用CE2和CE3。CE3的一部分被配置给OSD功能的同步操作和扩展的FPGA中的其他同步寄存器操作。

(2)EMIF端口。本系统设计一个64bit长的外部存储器端口。将地址空间分割成了四个芯片使能区,允许对地址空间进行8bit、16bit、 32bit和64bit的同步或不同步的存取。DM642板使用芯片使能区CE0、CE1和CE3。CE0被发送给64bit的SDRAM总线。CE1被 8bit的Flash、UART和FPGA功能使用。CE3被设置成同步功能。CE2和CE3都被发送给背板接口连接器。

(3)SDRAM寄存器端口。本系统设计在CE0空间连接了64bit的SDRAM总线。这32兆的SDRAM空间用来存储程序、数据和视频信息。总线由外部PLL驱动设备控制,运行在133MHz的最佳运行状态。SDRAM的刷新由DM642自动控制。 EMIF使用的PLL被称为ICS512,PLL的输入时钟是25MHz。DM642可以配置EMIF时钟的原始值。ECLKIN针脚一般为默认值,但其也可通过分频CPU时钟,来控制EMIF的时钟频率。在复位时,通过对ECLKINSEL0和ECLKINSEL1针脚的操作进行设置,其与EA19和 EA20针脚共同分享EMIF的地址空间。

(4) Flash寄存器接口 本系统设计4M的Flash,映射在CE1空间的低位。Flash寄存器主要被用来导入装载和存储FPGA的配置信息。DM642评估板的CE1空间被配置成8bit,Flash寄存器也是8bit。由于CE1的可利用地址空间小于Flash的空间,所以利用FPGA来产生3个扩展页。这些扩展的线形地址通过FPGA的Flash的基础寄存器进行定义地址,复位后默认是000。

(5)UATR接口。 双重的UART寄存器被映射在DM642的CE1空间的高位,随同FPGA异步寄存器一起。每一个UART,A和B产生8位的地址。本系统设计将CE1空间配置成8位存取。

(6)FPGA异步寄存器端口 。FPGA有10个定位在CE1空间高位的异步存储寄存器。这些寄存器实现的各种功能由于篇幅所限不再详叙。FPGA同步寄存器端口 FPGA在CE3地址空间开设同步寄存器。这些寄存器主要实现OSD功能和一些评估板连接。

(7)EMIF缓冲器/解码器控制 。EMIF缓冲器和解码器的功能通过GAL16LV8D普通逻辑数组驱动器实现,U15。驱动器可以对Flash进行简单的解码处理,UART与缓冲器共同控制CE1、CE2和CE3。

(8) 视频端口/McASP端口 。本系统设计有3个板上视频端口,这些端口可以根据可选择性功能,进行再分类,例如端口0和端口1的McASP和SPDIF功能。DM642使用所有的三个视频端口,视频端口0和视频端口1被用作输入端口,视频端口2用作显示端口。在标准配置中,视频端口0和视频端口1根据使用在McASP功能下进行再分类,连接到TLV320AIC23立体声编解码器或连接到SPDIF输出接口J9。

(9)视频解码器端口 。本系统设计可再分的视频端口0和视频端口1被用作捕获输入端口,命名为捕获端口1和捕获端口2。这些端口连接到SAA7115H解码器。视频端口贯穿 CBT开关,所以他们为了背板的使用可以被选择性的禁止。另一半的端口被连接到板上的McASP端口。捕获端口1通过一个RCA类型的视频插座J15和一个4针的低噪声S-Video接口J16,连接到视频源。输入的必须是合成的视频源,例如DVD Player或视频相机。SAA7115H是可通过DM642的I2C总线进行编程的,并且可以连接所有的主要合成视频标准,例如NTSC,PAL和 SECAM,这些都可以通过解码器的内部寄存器进行适当的编程。

评论