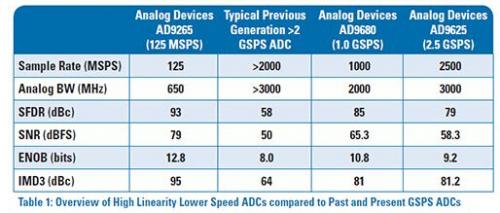

技术分析:时钟宽带GSPS JESD204B ADC

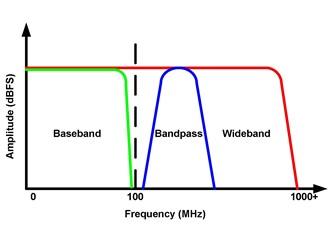

随着使用多模数转换器(ADC)的高速信号采集应用的复杂性提高,每个转换器互补时钟解决方案将决定动态范围和系统的潜在能力。 随着新兴每秒一千兆样本(GSPS) ADC的采样速率和输入带宽提高,系统的分布式采样时钟的能力和性能变得至关重要。 以高频测量为目标的系统解决方案,例如电气测量仪器仪表和多转换器阵列应用,将需要尖端的时钟解决方案。

本文引用地址:https://www.eepw.com.cn/article/201605/290788.htm选择专门的辅助时钟解决方案对防止ADC动态范围受限非常重要。 根据目标输入带宽和频率,时钟抖动可能会反过来限制ADC的性能。 转换器的高速JESD204B串行接口的低抖动和相位噪声、分配链路和对齐能力都是对优化系统性能极其重要的时钟属性。

支持带JESD204B输出ADC的多通道低抖动GHz时钟解决方案继续在业内激增。 设计工程师问我们该如何为其GSPS ADC选择合适的时钟解决方案。 下面就是答案和对与将时钟解决方案与特殊ADC配对产生的技术影响相关的部分常见讨论的分析。

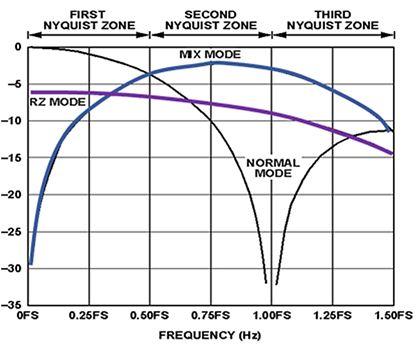

第2或第3奈奎斯特频率区域对宽带GSPS ADC使用高输入频率需要较低的抖动和高速时钟。 时钟抖动对ADC性能有什么影响?

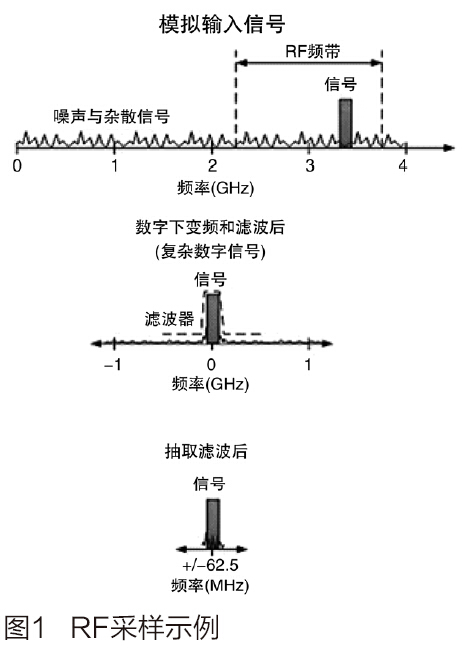

由于采用GSPS ADC和直接RF采样的系统中使用高频率输入信号,因此时钟抖动对系统性能的影响越来越大。 固定量的时钟抖动可能不会对具有低频输入的系统性能产生限制。 随着ADC输入频率提高,相同固定量的时钟抖动会对系统的信噪比(SNR)产生影响。 ADC的SNR定义为信号功率或噪声与输入ADC的总非信号功率的对数比。

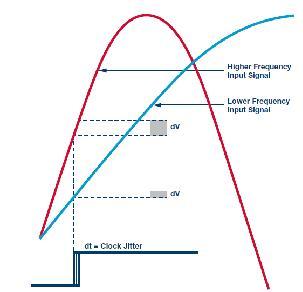

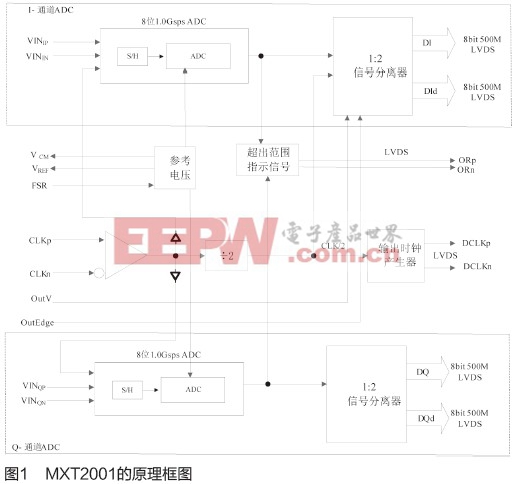

在较高频率下对快速上升时间信号进行采样时,具有已知量时钟抖动的ADC采样时刻将产生更大或更模糊的采样电压增量(dV)。 这是因为,高频信号的压摆率比低频信号大。 图1所示为这种关系的一个示例:

图1

ADC时钟出现固定量的时钟抖动(dt)后,更高频率的输入信号将具有一个更大的采样电压误差dV,此误差与更低频率的输入信号相关联。 这会对ADC的动态范围能力产生直接影响。

峰峰值和rms(均方根即平方)抖动之间的区别是什么?

时钟信号有两类抖动会直接影响ADC的性能: 随机抖动(RJ)和确定性抖动(DJ)。 确定性抖动源自一个可识别的干扰信号,其幅度大小是有界的。 它由所有其他无用信号特性产生,这些特性包括串扰、电磁干扰(EMI)辐射、电源噪声以及同步开关等周期性调制。 确定性抖动在时钟信号上将表现为杂散信号。 这些无用信号还会在ADC产生的数字频谱上表现为杂散信号。

随机抖动的大小没有界,而且是高斯抖动。 它可由较不可预测的影响产生,例如温度和小型半导体工艺变化。 如果ADC采样时钟上存在足够的随机抖动,则可能提高数据转换器上的噪声频谱密度(NSD)。 将每个RJ和DJ均方根的大小(RSS)相加便可以确定全部抖动对ADC采样时钟的影响。

典型时钟信号上的随机抖动大小直方图应为完全正常的高斯分布。 抖动的任何附加确定性分量都将产生双峰分布。 通过进行大量时序测量并确定最小和最大的抖动偏差,可测量峰峰值抖动。 随着更多测量的进行,最小和最大抖动将最终继续扩大绝对峰峰值。 有效的测量必须是固定的时间和测量样本数量。 因此,绝对峰峰抖动值并不是特别有用,除非是基于标准偏差已知的高斯分布。

均方根抖动是高斯曲线内一个标准偏差的值。 即使被测样本大小增加,该值也几乎不会变化。 这也意味着,均方根抖动值比峰峰抖动值更有意义,并且更易测量。 要使均方根抖动的大小有意义,总抖动必须是高斯分布。 变形的高斯分布图表示存在确定性抖动分量。 如果可能,应识别出确定性抖动分量的根本原因并将其缓和或消除。

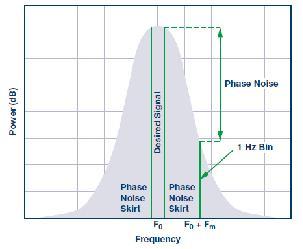

图2

尽管一个理想时钟信号的所有功率均应在单个频点内,但实际的时钟解决方案会有一些“相位噪声波裙”大小。 只有随机抖动的时钟信号将形成高斯分布。 任何确定性抖动都将使理想的高斯分布图变形。 曲线上任意点的相位噪声功率可从F0处的峰值到F0 + Fm处的目标频点测得。

ADC的输入时钟抖动将如何降低SNR和NSD的性能?

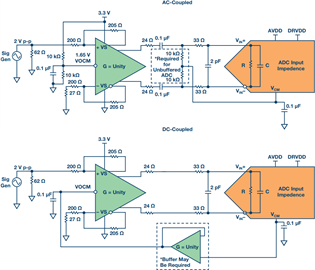

ADC的NSD是转换器的主要性能指标之一。 NSD定义单位带宽条件下的整个噪声功率(在相应ADC采样频率(fS)采样)。 NSD是ADC的满量程信噪比(SNRFS)与任意时钟抖动下降和噪声分布于频谱的奈奎斯特带宽(fS/2)的函数。 任意采样时间误差都将导致噪声信号功率的某些部分下降。

随着时钟抖动增加,目标采样信号功率的某些部分将以快速傅里叶变换(FFT)散布到其分立频点外,随后将变为噪声功率的一部分。 这是因为时钟信号相位噪声附近的信号的采样时间不理想。 图2显示了相位噪声“波裙”如何从频域中的理想目标信号泄放功率的直观示例。

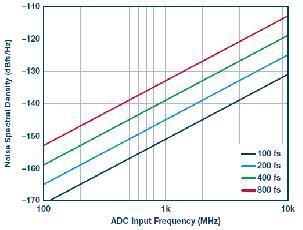

图3

以1 GSPS工作的ADC的理想NSD性能受rms编码时钟抖动限制。 时钟的均方根抖动可能会限制ADC在更高输入频率下的动态范围。

要得到ADC的总SNR下降值,应计算抖动噪声功率和ADC在目标信号频率下的标准SNR的和的平方根。 当ADC采样时钟抖动足够低时,SNRadc = SNR下降,因为转换器的内部孔径抖动和非线性将限制其SNR。 相反地,抖动逐渐增大的采样时钟将最终变成ADC SNR性能的限制因素。 这会越来越明显,因为目标信号的频率更高。 所有可实现ADC的输出噪声受SNR性能限制。 随着输入电平增大或减小,抖动噪声分量将相应地变化。

ADC的NSD可通过将ADC的满量程输入功率减去噪声功率的SNR下降值计算出,SNR下降值是奈奎斯特频率的函数。 通过下式可得出此值。

NSDADC = PowerADC_FS– SNR下降(dBFS) – 10log(fS/2)

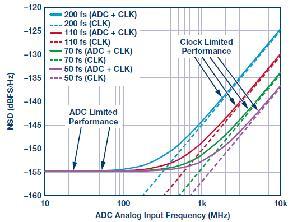

图4

此图显示了一个14位宽带转换器,该转换器在低模拟输入频率(<100 MHz)下被内部ADC量化和线性限制为–155 dBFS/Hz NSD,无论外部均方根时钟抖动是否达到200 fs。 这种情况下,系统时钟抖动将根据其均方根幅度确定高模拟输入频率(>100 MHz)下的NSD性能。

评论