技术分析:时钟宽带GSPS JESD204B ADC

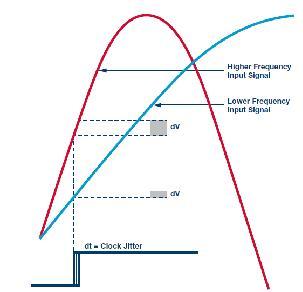

通过将每个1 Hz偏移点相加来尝试计算准确的抖动不太实用。 因此,通过以端点之间的dB/十倍频程值得到每个十倍频程各自的相位噪声斜率,可得出非常接近的均方根抖动。 理想情况下,宽带相位噪声会综合为一个较大的偏移,该偏移等于采样频率。 但是,要确保实例计算有界,我们可以在典型有线应用中计算均方根抖动。 我们来看看图6中的相位噪声曲线,计算983 MHz载波的10 kHz到20 MHz偏移内的抖动。

本文引用地址:http://www.eepw.com.cn/article/201605/290788.htm

图6

可将从图5中得出的相位噪声十倍频程分段曲线细分为三个分段,以计算983 MHz频率载波的10 kHz到20 MHz偏移之间的均方根抖动。

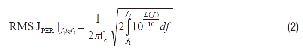

总均方根抖动是两个目标频点之间的曲线下方区域的和。 这种情况下,估计区域显示在标记为A、B和C的三个分段中。每个分段端点之间的相位噪声曲线斜率可轻松估计出,随后将用于进行计算。 整个相位噪声频谱L(f)上的周期抖动JPER之间的关系如下所示:

(f2 – f1)之间的特定频段内的RMS JPER可由下式计算出:

L(f)的频率轴为对数标尺时,可使用分段函数估计出相位噪声。 因此,L(f)可改写为:

其中,K-1是分段函数中的分段数,b是十倍频程起始频率的相位噪声大小,a是单位为dB/十倍频程的估计斜率,U(f)是阶梯函数。

如果我们将公式3中的L(f)代入公式2,便可以得到:

然后便可使用图6曲线的每个分段的值计算出均方根抖动,其中fc = 983 MHz:

A: a = –3.44 dB/十倍频程,起始频率为f = 10 kHz、b = –116.91 dBc/Hz

B: a = –9.75 dB/十倍频程,起始频率为f = 100 kHz、b = –120.35 dBc/Hz

C: a = –18.58 dB/十倍频程,起始频率为f = 1 MHz、b = –130.1 dBc/Hz

RMS JPER = 151 fs

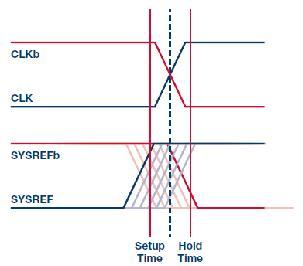

最新的GSPS ADC使用JESD204B串行输出代替LVDS输出的多路复用器组。 时钟解决方案还能如何使用JESD204B将系统内的多个ADC对齐到单个样本?

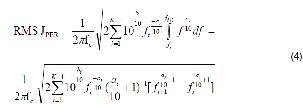

多通道低抖动GHZ时钟解决方案可将系统基准时序信号与称为SYSREF的信号在JESD204B规格内定义的相应时钟输出配对。 SYSREF信号是系统内使用的JESD204B链路的绝对时序基准信号。 多个仪器、传感器阵列和雷达系统都需要将多个同步ADC(2、4、8、16 … 100s)的时间对齐到尽可能少的样本范围内。 对于此类应用,时钟解决方案的时序灵活性对去偏斜和对齐SYSREF信号到每个相应的ADC时钟非常重要。

图7

多时钟输出配对在与彼此相关的相位及其关联的辅助SYSREF信号中可能会偏斜。 粗调和精调时序可使时钟和SYSREF在一系列ADC中同步。

具有16个ADC的系统可能需要四个独立的采集板,每块板使用四个ADC,并且通过电气背板直接连接在一起。 根据其相对于彼此的空间位置和走线之间的交点,每个ADC可在不同的时间看到关联的采样时钟边沿时刻。

在某些情况下,时钟和关联SYSREF需要对齐到各ADC的同一时间点。 在其他系统中,时钟相位需要刻意不对齐,以考虑一系列ADC之间的输入信号相位差异。 对于两个或四个ADC的交叉,时钟可能需要颠倒或针对特定90°增量调整相位。 无论如何,JESD204B时钟解决方案均可在每个ADC时钟和SYSREF配对之间提供独立的偏斜能力,以发挥采集系统的作用。

图8

对于JESD204B ADC和DAC,新的时钟芯片解决方案能够将多个输出对齐到一个单次或周期性SYSREF信号。 此功能可消除由ADC采集时间和时钟源之间的空间时钟路由延迟产生的传播时间差异。

GSPS ADC提供哪些时钟解决方案?

GHz时钟解决方案的相位噪声或时域抖动是为GSPS ADC选择时钟源时考虑的主要性能因素。 对于需要大量ADC的采集系统,最佳的时钟解决方案还需要提供大量输出通道以实现其各自的编码速率。 一个次要性能因素是在JESD204B链路内使用系统基准参数时的同步能力,此能力可进一步增强时钟系统的各项功能。

AD9525提供七个均方根抖动仅为50 fs的3.3 GHz输出时钟配对,以及在JESD204B接口的框架内部可用作SYSREF专用同步输出。

AD9528不仅提供七个1 GHz输出时钟配对,而且提供辅助SYSREF信号,这些信号的每个时钟配对均可去偏斜,以在单个采样对齐脉冲内对齐相应的ADC。

HMC7044是一款高性能的3 GHz 14输出抖动衰减器,附带JESD204B SYSREF支持。

结论

最新高带宽和宽带ADC的编码时钟相位噪声和抖动的幅度需要逐渐减小。 尽管可选用许多时钟解决方案与这些高频ADC一同使用,但那些目标带宽具有极低相位噪声并且能够同步许多ADC的解决方案才是最佳的解决方案。

典型时钟解决方案的相位噪声曲线可转换成时域,以确定均方根抖动和对ADC动态范围的潜在影响。 高级时钟解决方案的另一个优点具有能够在JESD204B框架内对时钟信号配对去偏斜的独特SYSREF。 为GSPS ADC选择的关键辅助时钟元件可能会维持或降低ADC的性能,具体取决于目标采集信号频率。

评论