技术分析:时钟宽带GSPS JESD204B ADC

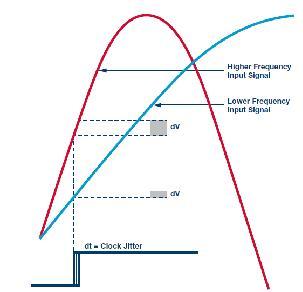

例如,图4显示了宽输入带宽具有多种时钟抖动的14位1 GSPS ADC的NSD影响。 对10 MHz至100 MHz的信号进行采样时,即使200 fs的极高时钟抖动也不会明显削弱ADC的NSD性能(–155 dBFS/Hz)。 但是,对1 GHz或2 GHz的输入信号进行采样时,与低rms时钟抖动相比,该时钟的200 fs 均方根抖动将明显限制ADC性能。 对2 GHz信号进行采样时,200 fs的均方根抖动将导致与目标信号功率相关的ADC噪声增大12 dB(与50 fs的均方根时钟抖动相比)。

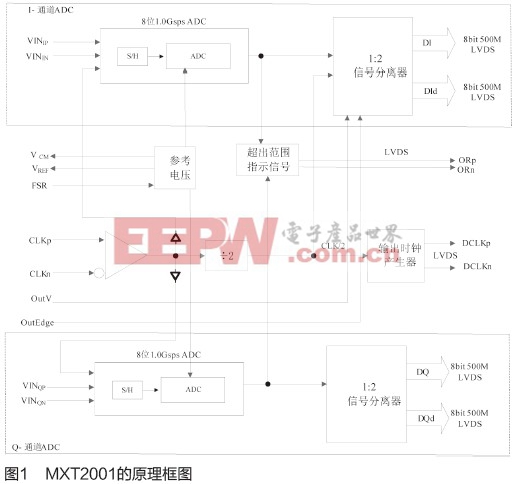

本文引用地址:http://www.eepw.com.cn/article/201605/290788.htm部分GSPS ADC可使快速输入时钟倍数在ADC内部分割,以得出实际的采样时钟。 在这种情况下对ADC使用更高速率的采样时钟的优势和劣势是什么?

与仅允许一个选项以1×实际采样速率输入时钟频率不同,部分ADC允许使用更高倍率的时钟速率,例如2×、4×或8×采样速率。 然后可对ADC进行配置,将更高频率的时钟从内部分割为将模拟信号采样到ADC的更低时钟倍率。 此类配置有几个优点。

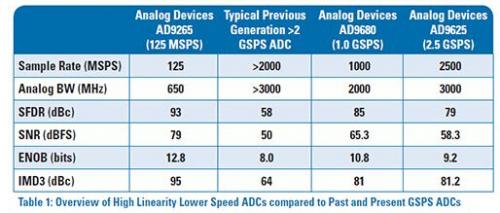

第一个优点就是系统板现可使用相同的硬件和时钟解决方案应付多个采样速率。 在这种情况下,使用较快或较慢采样速率只需要略微更改ADC的软件寄存器即可。 例如,以最高时钟速率使用ADC的电气测试和测量解决方案,如数字采样示波器,现在只需触摸GUI按钮,就能为最终用户提供多种采样速率选项。 如此,还可对仅存在软件版本差异的相同电路板进行市场细分。 提供此特性的两种ADC为AD9680和AD9234,即分别具有14位和12位分辨率的1 GSPS转换器。

第二个优点是,与使用更低的1×采样速率相比,使用更高时钟频率的ADC性能更高。 更高频率的时钟提供更快的信号压摆率,因此本身具有更精确的边沿和更低的抖动。 如前所述,假设ADC抖动不是限制性能的因素,则更低抖动的时钟本身可实现更低的NSD和更高的SNR。

第三个优点是,可消除计时装置和板上走线的一个附加时钟频率。 这使得系统能够以更小的时钟信号倍数工作,并且降低了整体计时复杂性。 RF时钟信号可能被用作允许较慢采样时钟使用内部分割功能的部分ADC的输入。

这种采样配置的一个潜在难题是需要确定能够在增大的频率倍数下实现低抖动的实际计时装置。 由于具有更高频率、性能和通道数的时钟解决方案已经发布并应用于系统板,此难题在某种程度上已经缓和。 但是,对更高采样速率转换器和复杂配套时钟装置的无止境需求依然没有减少。

我该如何从时钟装置获取频域相位噪声曲线并确定特定ADC采样时钟频率的时域均方根抖动?

尽管这两者描述了同样的现象,但将时钟的相位噪声与特定抖动值相关联可能有点违反常理。 虽然这两者相关联,但工程师需要跨越频域和时域鸿沟才能进行对应。 相位噪声曲线在频域中绘制,而时钟信号的均方根抖动分量反映为时域值。

时域中的乘法类似于频域中的卷积。 时钟上的任意相位噪声波裙或相位调制杂散噪声将卷积为数字信号提供给ADC。 耦合至采样输出的时钟上的噪声卷积的水平或大小如下式所示。

采样输出

时钟

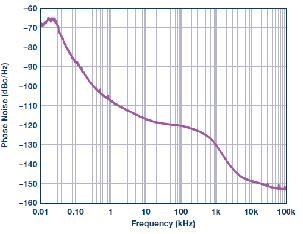

图5中的频域显示了时钟信号的一个相位噪声曲线示例。X轴显示了相对于载波的频率偏移,此例中为983 MHz的时钟。 Y轴是以dBc/Hz表示的相位噪声密度(与单位为赫兹的载波功率相关的dB功率)。 从此曲线应该能够清楚看出,以时钟上的频率进一步观察相位噪声时,将会创建相关噪底并减小逐渐增大的累积相位噪声的幅度。

图5

此曲线显示了与频率为983 MHz的载波时钟上的频率偏移交叉的相位噪声,其单位为dBc/Hz。 通过此信息可推算出时钟抖动。

时钟信号的均方根抖动可通过相位噪声曲线计算出,方法是将曲线下方的区域以每十倍频程分段的方式积分。 尽管现在有在线计算工具可从相位噪声计算出抖动,但使用几个数学公式也可做到这一点。

评论