多并行处理器接收机设计与实现

板上有两片C6416T,它们在结构上完全对称,描述上称两片C6416T及其外围资源为C6416T模块。C6416T模块中对称的结构决定了两片C6416T既可以是串行流水方式的并行计算,也可以是并发操作方式的并行计算,具体的方式由接收机板完成的算法来决定。两片C6416T通过双端口存储器(DPRAM)以共享存储器的方式耦合在一起,来完成处理时两者之间的数据共享和通讯。双口存储器数据总线宽度为64 b,容量为9 Mb。另外,两片C6416T之间还可以通过多功能串口(McBSP)进行数据传输,而且每片C6416T外围配备有1 024 Mb的SDRAM和64 Mb的FLASH。其中,大容量的SDRAM可用来暂存大量的中间处理数据;大容量的FLASH可用来存储大量的程序和非易失性数据。这里设计的存储器最大存储容量比较大,主要是基于通用性的考虑,配备不同容量时可以满足不同的应用需求,这可根据实际的情况而定。除此之外,板上还有两片3C120及其外围资源,描述上将其称为3C120模块。3C120模块中两片3C120之间也通过9 Mb的DPRAM来完成两者之间的数据共享和通信,而且两片3C120之间还通过自定义I/O扩展总线接口来进行数据通信与传输。另外,每片3C120与各自平行对应的C6416T之间通过EMIFA总线和SPI进行数据传输,与所对应的两路10 b ADC相连,以完成对接收中频数据的采样。

2 模块的设计

接收机板中,C6416T和3C120是核心器件,其他器件都是外设,以下的描述将围绕C6416T和3C120两个模块展开。

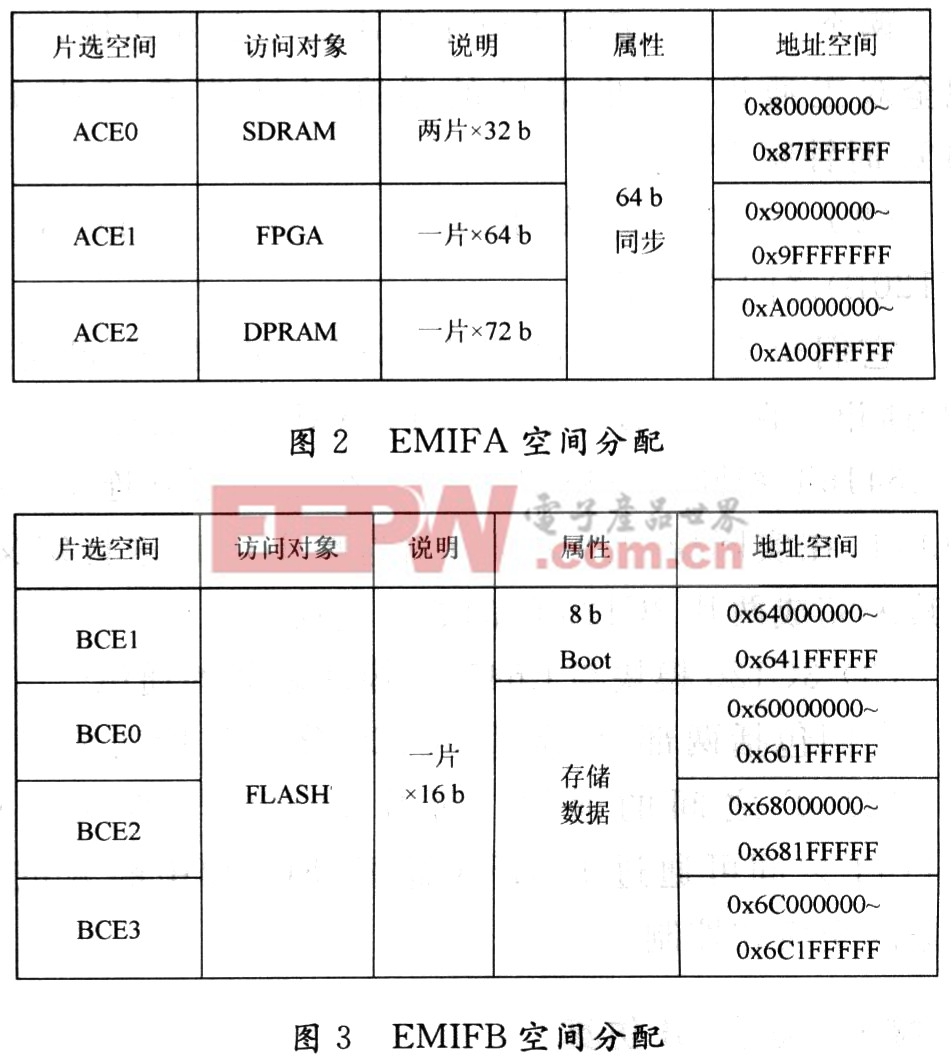

C6416T模块中主要的外设都与EMIF相连接,所以外设接口的设计主要介绍EMIF的设计。C6416T有两个EMIF接口,EMIFA的外总线上连接了FPGA,SDRAM和DPRAM,它们的数据宽度都是64 b。出于信号完整性考虑,外总线通过匹配电阻来解决信号反射的问题。FPGA用同步时序访问,SDRAM和DPRAM都是同步器件,它们被直接连接到临近EMIFA口这一级总线上,这一级总线的访问速率高,称为高速总线。EMIFA的每个CE空间最大的存储管理能力是256 Mb,外接4片32 b数据宽度、512 Mb的SDRAM时,可以达到这个最大容量,本设计电路中每个C6416T用了两片32 b数据宽度、512 Mb的SDRAM,占用一个CE空间,共1 024 Mb。另外,所选DPRAM芯片数据宽度为72 b,为了能与EMIFA总线匹配,在电路设计中将DPRAM的数据线每取8 b就间隔1 b,这样就得到64 b的数据宽度。

EMIFB的外总线上连接了FLASH,它的数据宽度为16 b,存储容量为64 Mb。因为EMIFB对8 b的异步存储设备的管理能力只有1 Mb,所以接8 Mb的FLAsH需要做地址扩展,这个扩展功能在CPLD中完成。在该接收机板中EMIFB的BCE1空间所对应的16 Mb FLASH用来做8 b Bootloader,剩余的48 MbFLASH用来存储重要数据。每个C6416T的EMI-FA和EMIFB的存储空间分配如图2和图3所示。

评论