基于FPGA的RS485接口误码测试仪的设计和实现

目前,通常使用的传统误码测试仪虽然具有测试内容丰富、测试结果直观等优点,但是由于通信系统复杂程度的不断增加,接口形式变化多样以及一些非标准码率的应用,使得传统误码测试仪的使用受到了一定的限制。另一方面,近年来FPGA技术得到了迅速发展,使用FPGA设计电路具有很大的灵活性,可以大大提高集成度和设计速度,还可以简化接口和控制,有利于提高系统的整体性能和工作可靠性。本文即介绍了一种基于FPGA的RS485接口误码测试仪的设计和实现。该设计具有系统简单、功能可靠、接口独特等特点,并且增加了传统误码测试仪所没有的测量系统传输延时的功能。

1 设计背景

本文所设计的误码测试仪主要用于测试某通信系统的误码性能。该通信系统是一个庞大复杂的系统,本文主要介绍信道部分,包括基带的信道编解码和无线信道的收发,其基本框图如图1所示。

为了在线路传输上保证良好的抗干扰能力,系统采用了RS485接口,选用了4.096 Mb/s的码率。因此,为了测试图1所示系统的误码性能,误码测试仪必须具有以下指标:

(1) 逻辑接口:RS485差分信号。

(2) 物理接口:DB9。

(3) 码率:4.096 Mb/s。

传统误码测试仪通常都不具备以上3项指标,本文设计的误码测试仪满足了上述3项指标。

2 误码测试原理

构成误码测试仪的方案有多种形式,其基本工作过程可以概括为以下几个步骤:

(1) 以某种方式产生和发送码组相同的码形,以相同相位的本地码组作为比较标准。

(2) 将本地码组与接收码组逐个进行比较,并输出误码脉冲信号。

(3) 对误码脉冲信号进行统计,并给出相应的误码率。

在通信工程应用中,为了最大程度地模拟真实通信中的数据流的统计特性,通常采用二进制伪随机序列。对于伪随机序列有以下几点要求[2]:

(1) 应具有良好的伪随机性,即应具有和随机序列类似的随机性。

(2) 应具有良好的自相关、互相关和部分相关特性,即要求自相关峰值尖锐,而互相关和部分相关值接近于零。这是为了接收端的准确检测,以减小差错。

(3) 要求随机序列的数目足够多,以保证在码分多址的通信系统中,有足够多的地址提供给不同的用户。

根据本地码组发生器的构成方式不同,误码测试仪可分为多种类型,本文采用的是逐位检测式,其使用的码组为最大长度线形移位反馈寄存器序列,即m序列。其工作原理为:本地的m序列发生器产生的m序列和所接收的m序列进行逐位比较,若两个m序列同步,则比较器输出的是传输误码;若两个m序列不同步,则比较器输出的是由失步造成的误码。由于失步造成的误码较大(根据m序列的特性,其误码率应为0.5),因此可根据误码率门限来区分检测系统是否失步。若失步,则让本地m序列发生器等待一个时钟周期,再依次逐位比较,并逐位控制本地m序列发生器的等待时间,直到两序列完全同步为止。

3 硬件设计

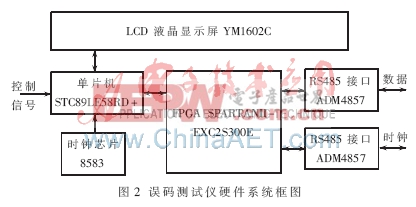

本系统用单片机作为主控芯片,由FPGA完成误码测试的工作,将得到的误码信息传送给单片机,单片机进行误码率的计算后送液晶屏进行显示。m序列的发送和接收都是通过RS485接口进行的。本系统单片机选用的是51系列的STC89LE58RD+,3.3 V供电,可以减小系统功耗。FPGA选用了Xilinx公司的SPARTNANII-E系列的XC2S300E,其内部包括了30万个逻辑门和其他丰富的资源,可以满足本系统的需要。RS485接口芯片选用Analog Device公司的ADM4857,它是一款10 Mb/s码率、全双工的485接口芯片[3-4]。系统的硬件框图如图2所示。

4 软件设计

软件部分是该系统功能实现的核心,主要包括了单片机和FPGA两大部分。

(1) 单片机软件

单片机作为该系统的主控芯片,主要完成FPGA通信控制、误码率计算、液晶显示控制等功能。开机后,单片机控制系统进入挂起状态,等待按下start按钮。开始工作后,单片机每隔1 s向FPGA请求刷新1次误码数据,FPGA则将误码数据通过SPI总线传送给单片机。单片机将取得的误码数据换算成误码率连同得到的系统传输延迟时间一起送到LCD显示。单片机软件的流程图如图3所示。

评论