测量磁盘驱动器柔性电路的互连阻抗测试

HDD中需精心设计的链路是位于前置放大器和读/写磁头组件之间的互连。该互连是确保HDD以多倍Gb/s的速率读写大量数据关键组件,但是,诸如交调失真、过冲和下冲等影响常会降低互连的性能,本文简要介绍如何利用时域反射测量仪器对该互连阻抗进行测量。

本文引用地址:https://www.eepw.com.cn/article/193861.htm

HDD中需精心设计的链路是位于前置放大器和读/写磁头组件之间的互连。该互连是确保HDD以多倍Gb/s的速率读写大量数 据所要求的速度和控制的关键组件,但是,诸如交调失真、过冲和下冲等影响常会降低互连的性能,并大大地耽误设计进程,甚至影响产品性能或推迟上市时间。

面对这一挑战,3M亚太公司的工程师们正将电子设计自动化(EDA)技术融入到整个设计周期当中,从而使HDD柔性互连在满足开发时间和成本目标的同时确保其性能的先进性,他们通过仿真获得的结果已经用时域反射测量仪器(TDR)加以验证。

设计所面临的挑战

在本文的设计中采用EDA工具的动因是缩短设计产品及上市所需的大量时间,并实现更为鲁棒的设计。鲁棒性是通过让设计-布局-分析-除错一整套操作过程更频繁地和更快地执行来实现的,与制造和测量原型样机相比,成本得到了显著的降低。

3M Microflex电路是一种置于衬底上的薄而轻的信号布线,该衬底具有精确设计的电路特征。它们用于IC封装、HDD、医学设备、打印机和其它的高密度应用。柔性电路技术使得产品更小、更轻和运行更快,并能降低总的应用成本。

本文要测量的电路是一种柔性悬浮结构(FOS),该结构用于一种HDD万向架装配头(HGA)。设计指南包括三个方面:机械兼容性、加工的独立性和电性能。

1.HGA机械兼容性:在万向架组件区域,HGA的强度必须最小以确保磁头与记录媒体的飞行高度兼容,这就要求降低电路的导体高度,因此,会影响整个电路的阻抗。

2.加工的独立性:3M公司目前的加工能力为25微米线宽和线间距。

3.电性能:整个柔性电路要求从驱动器芯片输出到巨磁阻读/写头的阻抗受控。

FOS设计和分析

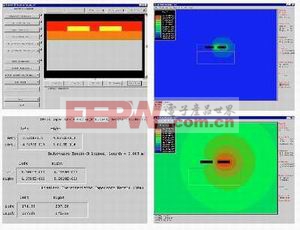

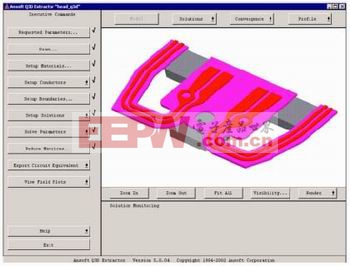

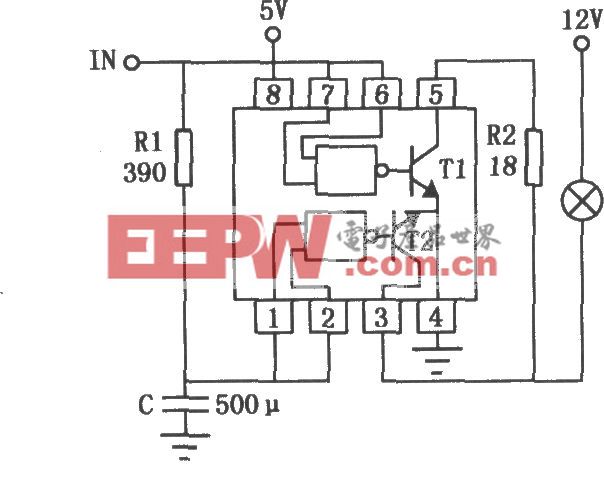

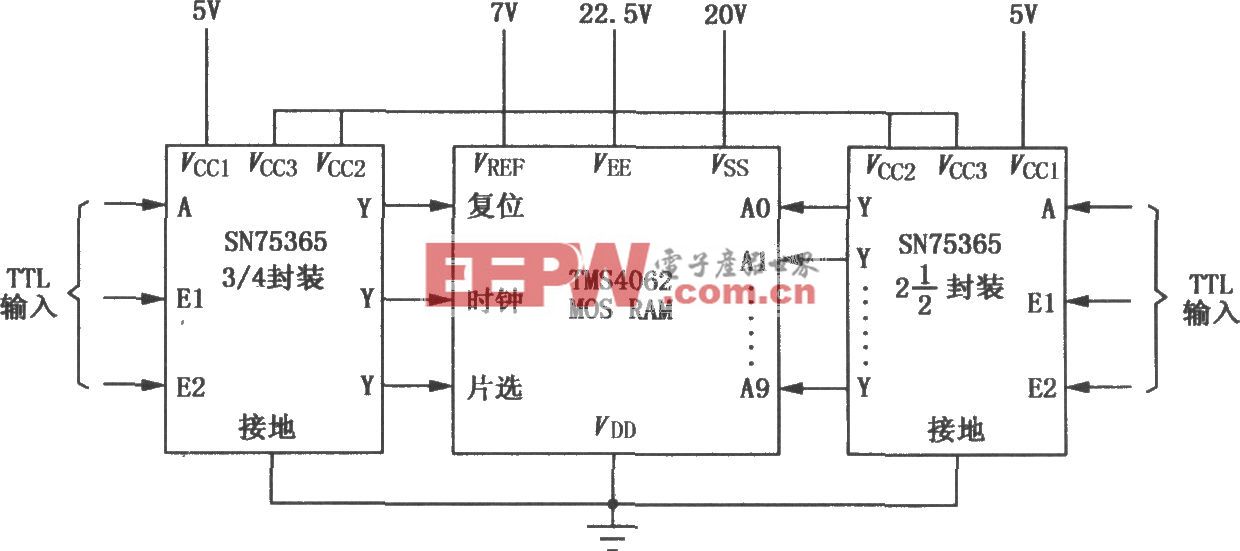

阻抗(R)、电感 (L)、电容(C)和电导(G)的提取是利用Spicelink来完成的,它是Ansoft公司提供的一种电磁场解算器。FOS(图1)装配不同层的堆叠 是在内置的2D建模工具内闯建的。堆叠的每一层被赋予不同的材料特性,包括线宽、衬底、粘合剂、钢结构支撑等。

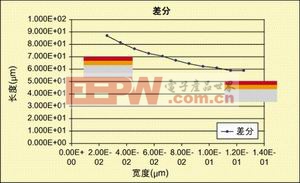

Spicelink的变参量功能使工程师能够对线间距和堆叠组合变化的影响进行研究,从而根据“什么-如果”假定来评估各种 变化对电路性能的影响。图2显示了一系列仿真的视图。图2上左显示了这种堆叠组合的横截面,图2下左显示了采用2D提取器计算出的RLCG矩阵,图2上右 和图2下右显示了由仿真器产生的电磁场图。图3中参变量研究的结果显示了线宽和线间距对FOS柔性电路阻抗的影响。

通过TDR提取阻抗特征

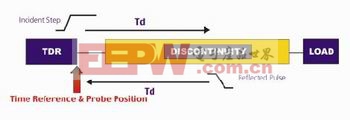

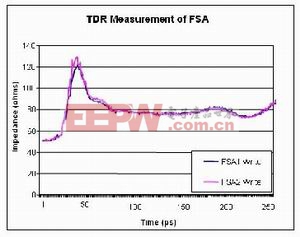

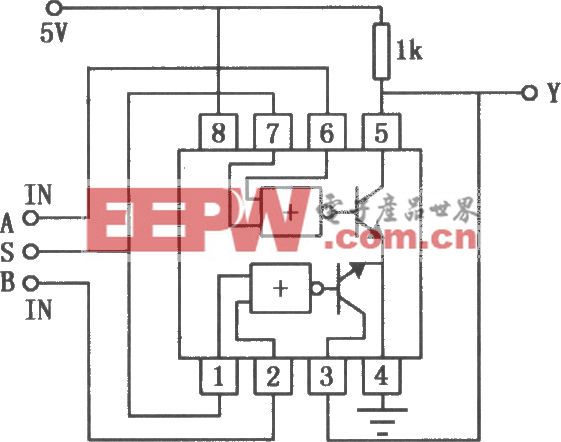

TDR可用于测量柔性结构的阻抗特征。虚拟TDR可通过执行一系列从EM仿真提取模型的运算,然后利用SPICE电路仿真器进行时域仿真来实现。仿真结果与从TDR仪器所测得的实验结果高度一致。

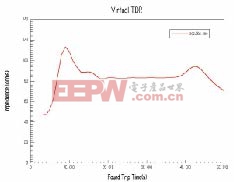

图4阐明了TDR测量的原理。电路的阻抗特征由反射波形绘制而成。TDR结果表明:沿大部分信号传输路径的阻抗被控制在75-80 欧(图 5)。这将确保因电路的阻抗失配造成的反射被抑制在足够小的范围内,从而确保电路正常工作的目标阻抗。如果反射无法减少,那么衰减和失真将使最终达到前置 放大器端的信号成为无法利用的信号。

交调分析

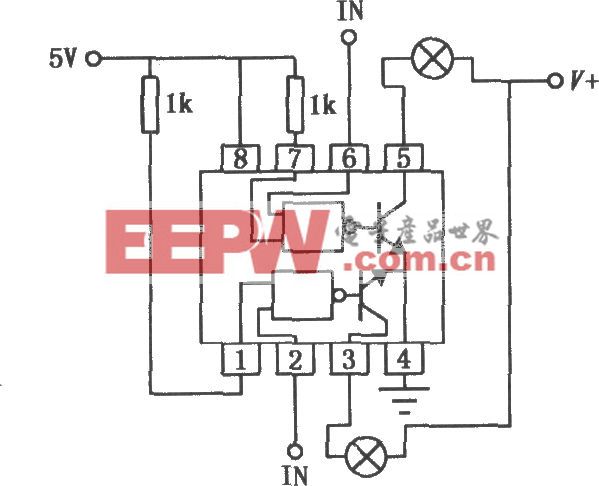

在FOS装配中需予以特别关注的是电路中写信道和读信道间的交调。对于一个50 ohm的电路,典型的读周期电流是5 mA的阶乘,这就意味着,要想HGA的读/写头不被损坏,要求读信道承受250 mV的最大电压。

要分析这一情形,需从3D EM模拟工具中提取出SPICE模型,重点分析FOS装配结构的关键区域(图 6)。图6中显示了HGA区域和电路的尾部。在电路模型被提取后,就执行时域仿真以确定交调电平。

图7显示了电路仿真产生的输出波形。如图8所示,FOS结构的交调电压电平落在最大的限制范围内。这些交调图有助于在保持足够性能前提下,保持FOS的尺寸尽可能的小,封装尽可能的密实,从而免受损伤磁头。

本文小结

通过执行柔性电路的参变量提取可以判定其性能。这些分析包括版图设计前传输线的特征阻抗仿真和版图设计后的交调、过冲和下冲分析。整个结构的阻抗特征可以通过执行虚拟TDR获得。此外,还测量了沿传输线和堆叠变化的阻抗。

典型的FOS原型的制造和测试周期包括在HGA上制造和装配柔性电路,这一过程需要5到6个星期才能完成。在设计过程中采用 Ansoft公司的 Spicelink技术,所耗时间将会有效地减少到4-5天。此外,在不需要增加与制造和测试相关的时间与成本的基础上,通过迅速进行容差分析,采用 EDA工具能够得到更为鲁棒的设计。

在交付生产前,预测新设计的性能可以确保识别并矫正不需要的电效应。在3M的柔性设计过程中引入Ansoft公司的EDA工具,极大地减少了成本并缩短了上市时间。

参考文献:

1. Howard W. Johnson, Martin Graham. High Speed Digital Design: A Handbook of Black Magic. Prentice Hall PTR, 1993.

2. Robert Dodsworth, George Hare. HGA Technology Driver-The Need for Speed. CleanRooms/DataStor Asia, 2001.

3. Eric Jensen, Mike Resso, Dima Smolyansky, Laurie Taira-Griffin. Improved Method for Characterizing and Modeling Gigabit Flex-Circuit Based Interconnects. DesignCon, 2001.

接地电阻相关文章:接地电阻测试方法

评论