基于DMA的大批量数据快速传输模块设计

对于调试模式下Nios II IDE的输出结果,如图5所示。由于测试数据太长,这里只给出测试数据的首部及尾部。图5(a)为测试数据的首部,使用printf()函数输出,第一个数据为2,接着是2,3,…,从图5(b)可看出最后一个有效数据是513,从512起的数据为0,这是数组的初始值,这与图4相对应。本文引用地址:https://www.eepw.com.cn/article/192791.htm

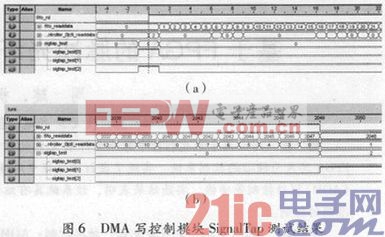

DMA写控制模块测试时,置FIFO数据宽度为16,NiosⅡ控制端口数据总线宽度为16,FIFO深度为2 048,在NiosⅡ软件中设置一个长度为2 048的数组,数组数据宽度为16位,初始化时把数据赋值为1~2 048的计数值,然后发起DMA写传输,把数据写入到DMA写控制模块中,在FPGA再用硬件语言读此外设中FIFO数据并在SignalTapⅡ中显示,其测试结果如图6所示。

图6中,fifo_rd表示FPGA中硬件逻辑读取DMA写控制模块的读信号,fifo_readdata是外设中FIFO的数据总线信号,sigtap_test信号连接至外设中FIFO满、FIFO空以及waitrequest信号(LSB),图6(a)表示了外部逻辑读取外设中FIFO的数据起始段,在读信号有效之前,sigtap_ test[2]信号是高电平,表示FIFO满,sigtap_test[0]为高,表示外设此刻不能响应DMA写入的数据,然后FPGA外部逻辑在检测到FIFO满后开始读取数据,在下一个时钟周期,FIFO数据总线上出现有效数据。图6(b)是读取FIFO时数据的结束段,最后一个数据为2 048,读取后,sig tap_test[1]为高电平,表示数据读空,这与NiesⅡ中软件写入DMA从而写入DMA写控制模块的数据是一致的,由此验证了模块设计的正确性。

5 结束语

设计方案稳定可靠、传输速度高,具有一定的通用性,能满足NiosⅡ与外设之间的大批量数据传输,具有广泛的应用前景,同时,使用了FIFO作为缓存,进一步提高了数据吞吐量,具有较强的实用价值。

评论