基于DMA的大批量数据快速传输模块设计

摘要 针对Altera公司SOPC解决方案中,DMA模块无法直接读/写FPGA外设的情况,提出了基于Avalon总线流传输模式的通用DMA读/写控制模块的设计,设计了两个自定义外设,实现了DMA对FPGA外设的高速数据存取和Nios II与FPGA大批量数据的快速传输。介绍了Avalon—MM总线规范,阐述了系统架构以及DMA读控制器的设计,测试结果表明,该方法是一种高效可行的解决方案。

关键词 SOPC;Nios II;DMA;Avalon总线

DMA控制器作为SOPC设计中使用频率较高的IP核,可用于存储器或外设间进行批量数据传输,以提高系统数据吞吐量。然而,由于DMA控制器只支持对基于Avalon总线流传输模式的外设进行数据传输操作,对用户自定义外设不予支持。文中提出了一种基于Avalon总线流传输模式的通用DMA接口控制器设计,实现了NiosⅡ与FPGA的大批量数据快速传输,显著提高了系统的数据吞吐量。

1 Avalon—MM总线规范

Avalon总线规范是为开发SOPC环境下外设而设计的,为SOPC设计者描述这些外设的端口提供了基础。Avalon总线有多种传输模式,其中,流传输模式为从端口提供了一种机制,用于控制来自主端口的传输,流传输模式的这些特点使其特别适合于DMA传输。

流模式从端口传输模式的信号,除了在从端口传输中使用的信号之外,又引入了3个信号:readyfordata、dataavailable和endofpack et。其中,从端口通过设置Readyfordata有效来表示它已经准备好接收来自Avalon总线模块的写传输;使readyfordata无效表示写操作将引起数据上溢;从端口通过设置dataavailable有效来表示它已经能够为来自Avalon总线模块的读传输提供数据,dataavailable无效时读操作将引起数据下溢;在任何传输期间,流模式从端口都可以设置endofpacket信号有效,并通过Avalon总线模式传输给主端口。对于endofpack et信号的解释取决于用户设计,必须明确外设如何响应endofpacket信号的变化。

2 系统结构

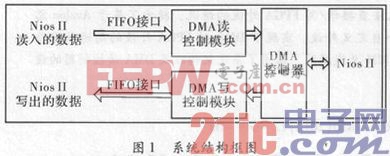

提出的NiosⅡ与外设进行大批量数据传输的结构如图1所示,当NiosⅡ需要从外设读入数据时,外设通过FIFO接口将数据写入DMA读控制模块,然后数据经DMA传输至NiosⅡ,反之,当NiosⅡ输出数据时,数据通过DMA传输至DMA写控制模块,FPGA逻辑通过FIFO接口从这个模块读取数据。DMA读/写控制模块的设计,是为了解决SOPC中DMA模块与FPGA片上FIFO不同接口间的数据传输问题,而在SOPC中,DMA模块使用的是支持流传输模式的Avalon—MM总线。DMA读/写控制模块主要完成两个功能:一是FIFO与DMA主端口之间的数据交互;二是作为一个NiosⅡ的外设,NiosⅡ处理器能够对此外设进行控制并能随时获取该外设的状态信息。

3 DMA读/写控制模块的设计

DMA读/写控制模块作为系统结构的核心,其结构框图如图2所示。此模块包括两个Avalon—MM从端口:一个作为DMA从端口,用于处理DMA对此模块的数据读操作;另一个Avalon—MM从端口是NiosⅡ的控制从端口,用于NiosⅡ处理器对这个模块进行控制并且随时获取此模块的状态信息。模块还包括一个中断请求信号(IRQ),当外设有数据需要读取时,可以使这个信号有效,从而通知NiosⅡ发起DMA读传输。另外,DMA读控制模块中还例化了一片FPGA片上FIFO作为数据上传FIFO,用于系统待上传数据的暂存。使用FIFO可以提高数据传输的吞吐量,同时简化FPGA硬件逻辑的操作,图2中的管道(Conduit)端口就是FPGA硬件逻辑操作FIFO的接口。

评论