基于Nios II内核的SOPC开发板的设计

随着 EDA 技术及微电子技术的飞速发展,现场可编程门阵列(Field Programmable Gate Array,简称FPGA)的性能有了大幅度的提高,FPGA的设计水平也达到了一个新的高度。传统的嵌入式系统设计方法已不能适应当前设计的需要。基于 FPGA 的嵌入式系统设计为现代电子产品设计带来了更大的灵活性,以 Altera 公司开发的 Nios II 软核处理器为核心的SOPC(System on Programmable Chip)系统便是把嵌入式系统应用在 FPGA 上的典型例子。

SOPC开发板的核心器件是Altera公司生产的Cyclone系列FPGA,其关键技术是在Quartus II、SOPC Builder及Nios IDE平台上实现可配置、可剪裁系统的设计。

1 Nios II软核处理器的特点

Nios II系列32位 RISC 嵌入式处理器具有很大的灵活性,可以在多种系统设置组合中进行选择,达到性能、特性和成本目标。其具有超过200DMIP的性能。

Nios II系列嵌入式处理器是一款采用流水线技术、单指令流的RISC CPU,广泛应用于嵌入式系统。Nios II 包括三种内核,即快速的 Nios II/f (最高性能的优化)内核、经济的 Nios II/e (最小逻辑占用的优化)内核以及标准的 Nios II/s (平衡于性能和尺寸)内核,每种内核根据不同的性能而优化。

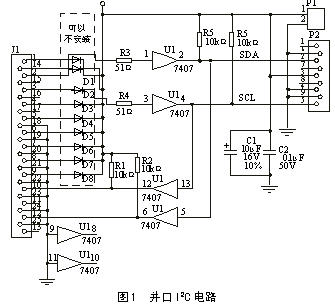

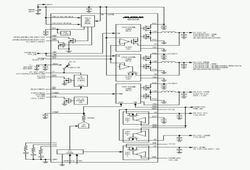

考虑到性能和成本,通常采用 Nios II 标准内核设计。Nios II 嵌入式CPU支持32位指令集、32位数据线宽度、32个通用寄存器、32个外部中断源、2GB寻址空间,包含高达256个用户自定义的 CPU 定制指令。其可选的片上 JTAG 调试模块是基于边界测试的调试逻辑,支持硬件断点、数据触发和片外片内的调试跟踪。Nios II 标准内核设计框图如图1所示。

图1 Nios II 标准内核设计框图

2 SOPC 技术的实现

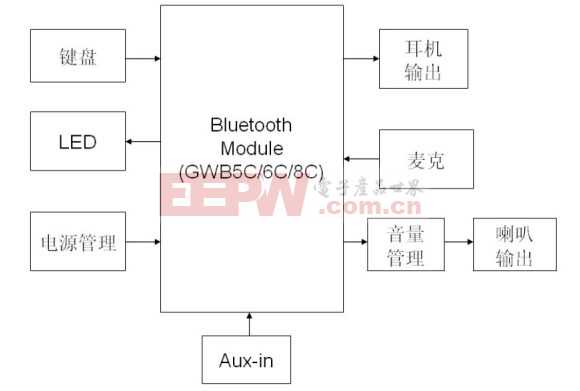

SOPC技术是一种灵活、高效的片上系统SOC设计方案,其工作环境是Altera Quarlus II中的SOPC Builder。与其他SOC设计相比,其优点在于可编程性,利用FPGA的可编程性进行SOC设计。通过采用SOPC Builder工具,用户可以很方便地将处理器、存储器和其他外设连接起来,组成一个完整的嵌入式系统。SOPC从内部的角度,主要包含两个部分:图形用户界面(GUI)和系统生成程序。图形用户界面内每个组件也可以提供自己的配置图形用户界面,GUI 创建系统PTF文件对系统进行描述;生成程序创建针对目标器件的系统HDL描述。利用SOPC Builder创建的GUI如图2所示。

图2 SOPC Builder GUI界面

SOPC开发板设计实例

SOPC开发板选择Cyclone系列器件EP1C3,该器件基于成本优化的全铜1.5V SRAM工艺,容量为2910个逻辑单元,59904比特嵌入式RAM,支持单端I/O标准,通过LVDS标准可提供104个信道的I/O支持。利用锁相环(PLL)可设计复杂的时钟管理电路。

1 开发板的硬件设计

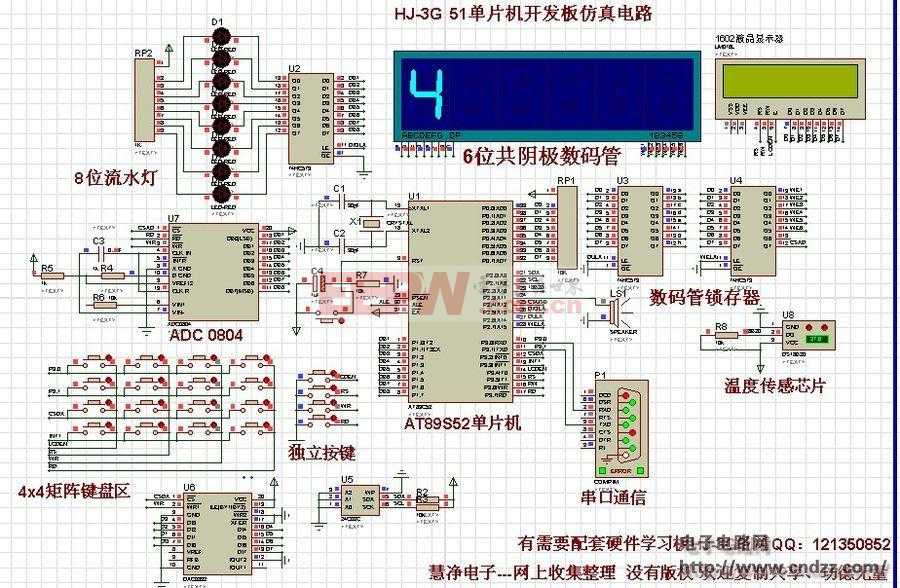

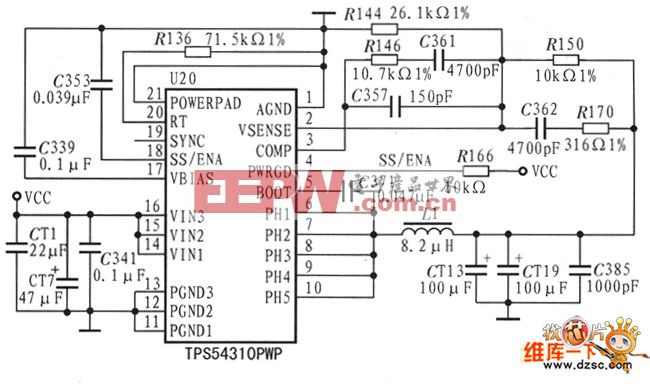

开发板主要包括以下几部分:4个七段共阳数码管、4个LED、2个RS232接口、1个USB接口、1个PS2接口、LCD接口(19264)、蜂鸣器和25MHz有源晶振,下载电路包括JTAG方式和AS方式,采用EPCS1作为串行配置器件。硬件原理框图如图3所示,下载电路如图4所示。

图3 开发板硬件原理框图

图4 JTAG与AS下载方式

2 Nios II内核设计实例

Nios II内核的设计是建立在Quartus II、SOPC Builder和Nios IDE等开发环境基础上的,Nios CPU内核设计流程如图5所示,生成的Nios CPU内核如图6所示。

图5 Nios CPU内核设计流程图

图6 Nios CPU内核实例

结束语

利用Nios II软核处理器的优势,在FPGA内部嵌入可定制的CPU,使用户可以根据需求来灵活的配置系统,即节约了成本,又加快了产品推向市场的速度,且易于升级改进。本文提出的基于Nios II内核的SOPC开发板的设计给 Nios II的应用提供了一个有效的硬件平台,具有广泛的实际应用价值。但由于EP1C3内部RAM资源有限,需外扩RAM和FLASH才能满足更多开发和应用。针对这个问题,开发板上已经预留出外扩接口,可以满足用户设计上更多的需求。

评论