VHDL实现PCM码解调程序模块设计

1 引言

本文引用地址:https://www.eepw.com.cn/article/192104.htm脉冲编码调制(Pulse Code Modulation,简称PCM)是一种概念简单、理论完善的编码系统,其最大特征是把连续的输入信号变换成在时间和振幅上都是离散量,然后再变换为代码传输。信息为数字信号,在远距离再生中继传输中不积累噪声,从而提高了通信系统的有效性、可靠性和保密性。利用现场可编程门阵列(FPGA)和VHDL 语言实现了PCM码的解调,这样在不改变硬件电路的情况下,能够适应PCM码传输速率和帧结构变化,从而正确解调数据。

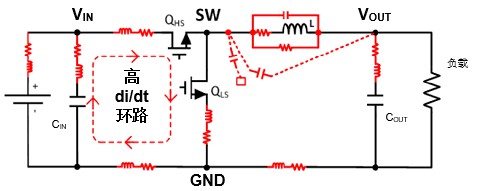

2 硬件电路设计

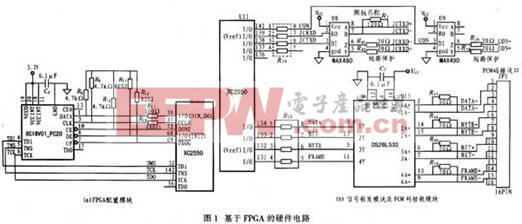

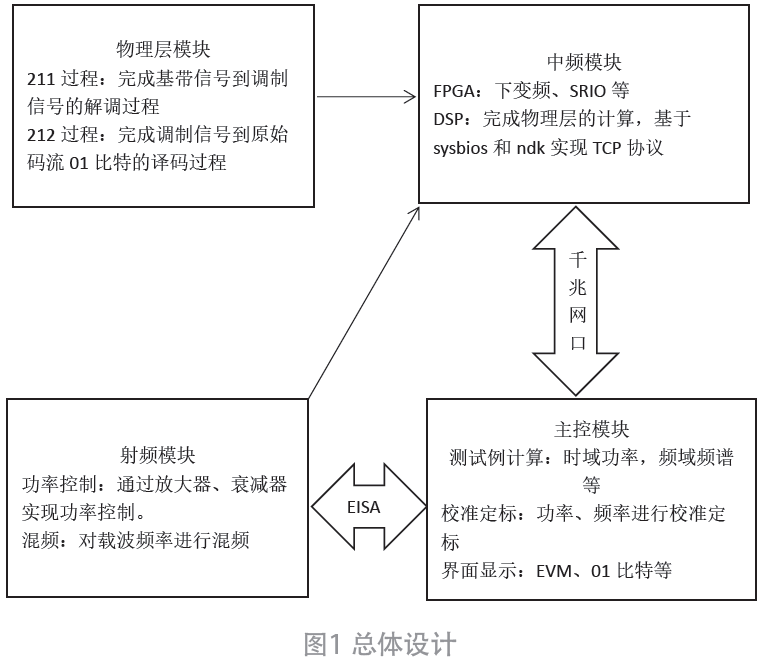

图1给出基于FPGA的硬件电路。其中,图1(a)为FPGA配置模块;图1(b)为信号收发模块及PCM码接收模块。

该系统设计中FPGA选取Xilinx公司的Spartan系列XC2S50器件。该器件有4种工作模式,分别为主串模式、从串模式、边界扫描和从并模式。将M0,M1,M2接地,使其工作在主串模式下。FPGA由存储在片内RAM中的程序设置其工作状态,工作时需要编程设置片内的RAM。用户可根据不同的配置模式,采用相应的编程方式。上电时,FPGA将EPROM中的数据写入片内编程RAM,配置完成后,FPGA进人工作状态。掉电后,FPGA内部逻辑消失,恢复成白片。因此,FPGA能够反复使用且无需专用的编程器,采用通用EPROM,PROM编程器即可实现。当需要修改FPGA功能时,只需换一片EPROM。同一FPGA根据不同的编程数据能够产生不同的电路功能。该系统在发送方接收到请求信号后则开始发送数据。PCM码解调模块在移位脉冲同步下接收数据,并将串行数据转换为并行数据存人FIFO中。每接收到一次请求脉冲发送一帧数据,每帧数据以146FH为结束标志字,EB90为子帧同步字,当PCM码解调模块检测到帧尾后停止解调,并停止向FIFO写人数据。PCM码解调模块由硬件描述语言编写并集成于FPGA中。

3 PCM码解调程序模块

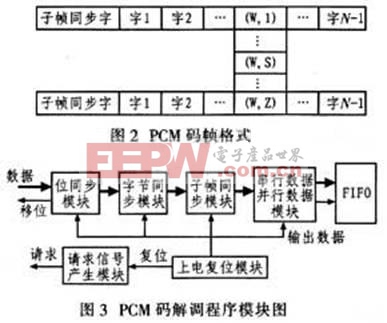

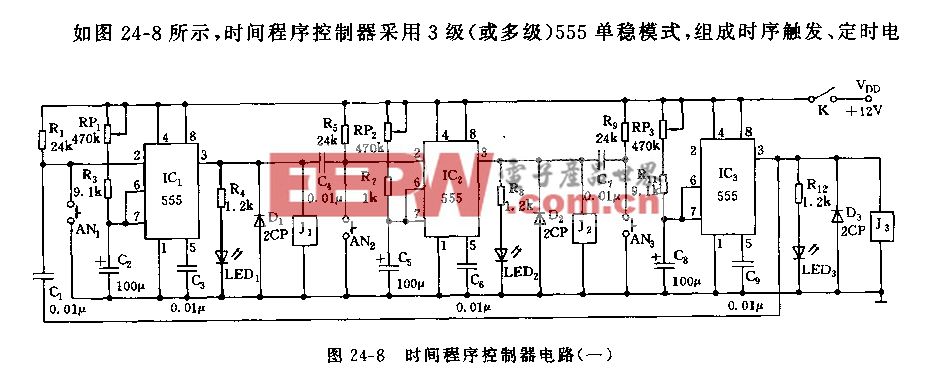

图2给出PCM码帧格式。其中N为子帧中的字数,最大值为1 024;Z为一帧所含子帧个数,最大值为256。子帧同步字字长为16~32 bit,字长度为4~16 bit。在遥测系统中,依照PCM码帧格式,将所要测控的参数放在格栅中自定义位,同时定义子帧同步字和字长。当发送请求信号,同步接收一帧数据,即使一帧数据接收错误,也不影响下一帧数据解调的正确性,进一步减小误码率。检测子帧同步字时,先找到一个子帧同步字后,每隔N个字节判断移位数据是否为子帧同步字,对每一个子帧都进行判断,即使第一次误判,或当PCM发送中断后再重发,也不会影响后续正确解调数据。可根据子帧同步字、帧尾标志字和请求信号的顺序由该解调数据模块进行自我纠正,从而大大降低了误码率。图3为PCM码解调程序模块图。

3.1 移位脉冲产生程序

系统设计要求移位脉冲频率为80 kHz,对时钟脉冲进行40分频。移位脉冲产生程序仿真图如图4所示。其中,bitt为位同步移位脉冲。

评论