基于CPLD的键盘控制器设计

0 引 言

由于CPLD的可再编程性质,可以将同一装置用于不同的键盘和产品,而收到高产量、低成本的效果,同时也节约了单片机的资源以做它用。可再编程的特点辅之简便易用的设计工具,使设计可以进行晚期更改,提高了产品设计的灵活性,降低了风险。在单片机应用系统中,利用键盘接口输入数据,是实现现场实时调试、数据调整和各种参数设置最常用的方法。单片机的外围键盘扩展电路有多种实现方式,例如直接利用单片机的I/O接口,或者采用8255A接口芯片,就可以实现外围键盘的扩展功能。但是,在这些方法中,键盘扩展电路需要占用单片机的资源对按键进行监控和处理,这对要求高实时性处理的单片机系统是不容易实现的。为了解决这一问题,可以使用专用键盘接口芯片来扩展键盘子系统。但是这类专用键盘接口芯片在使用灵活性方面尚有欠缺,尤其当用户需要实现某些特定功能时,其缺点更为明显。针对上述问题,在此提出一种基于Lattice公司LC4128V的4×4键盘接口芯片设计。采用的软件开发环境是IspLEVER。

l 开发环境介绍

IspLEVER是Lattice公司最新推出的一套EDA软件。设计输入可采用原理图、硬件描述语言、混合输入3种方式,它能对所设计的数字电子系统进行功能仿真和时序仿真。编译器是此软件的核心,能进行逻辑优化,将逻辑映射到器件中去,自动完成布局与布线,并生成编程所需要的熔丝图文件。软件中的Constraints Editor工具允许经由一个图形用户接口选择I/O设置和引脚分配。lspLEVER软件提供给开发者一个简单而有力的工具,用于设计所有Lattice可编程逻辑产品。

2 键盘控制器设计

2.1 基于LC4128V的4×4键盘控制器设计

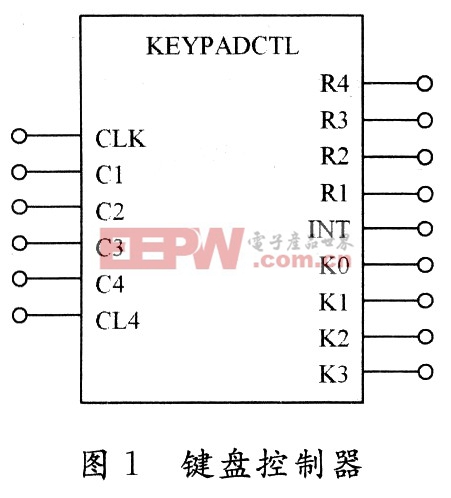

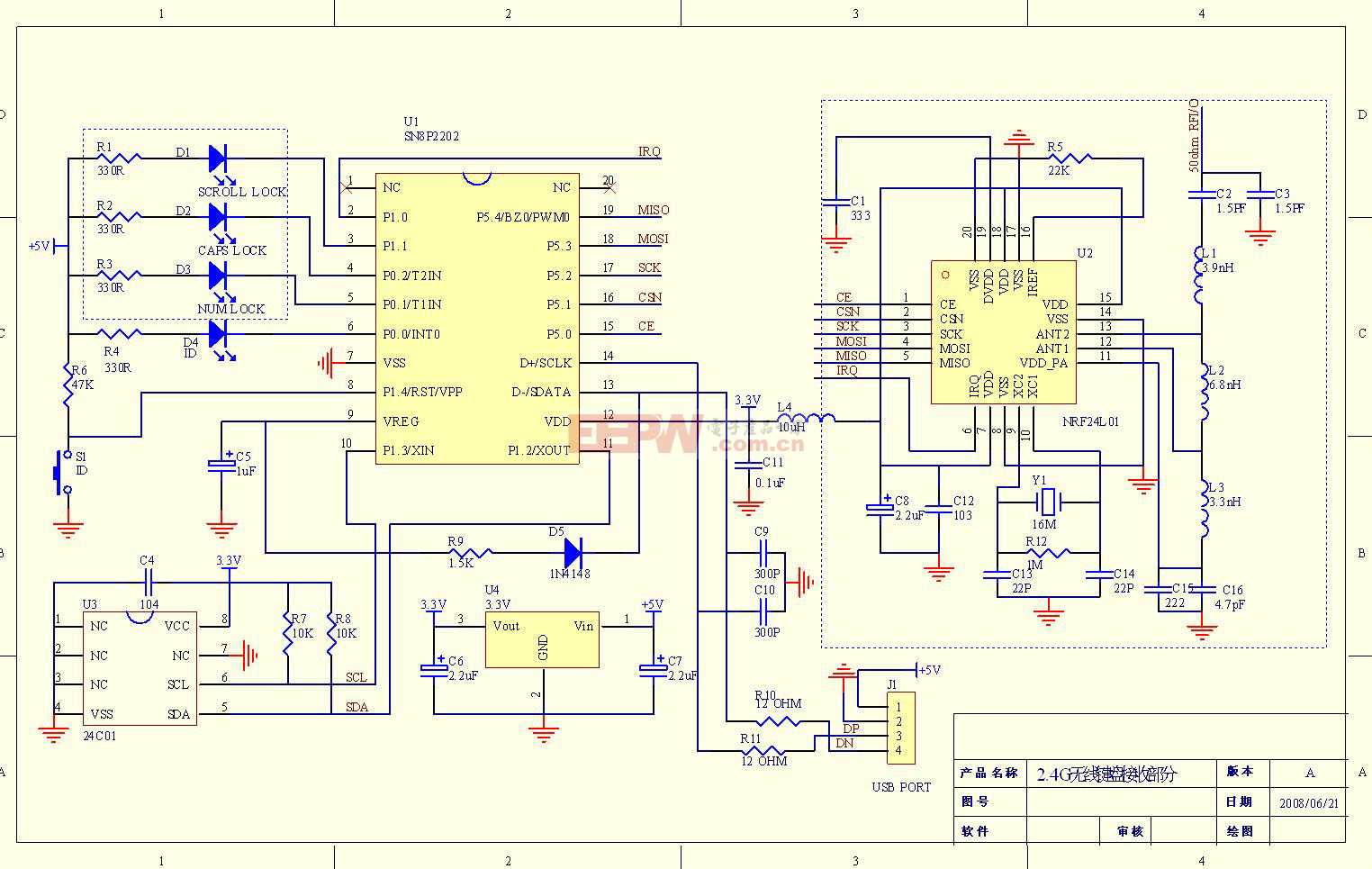

图1给出基于Lattice公司的可编程逻辑器件LC4128V的4×4键盘控制器(KEYPADcTL)设计。

根据键盘的扫描原理,键盘控制器的输出引脚R1~R4(行扫描线)依次循环输出低电平,并将相应的键盘行置低。当有按键按下时,相应的输入c1~c4(列回复线)也被置低。然后根据行和列的低电平对应关系就可以通过编码确定按下的键值。输出K0~K3就是最终等待单片机读取的键值。INT输出单片机的中断信号,通知单片机来读取键值。CLK是控制器的时钟信号,cLR是控制器的清零复位信号。

2.2 内部原理图及其主要部分的工作原理

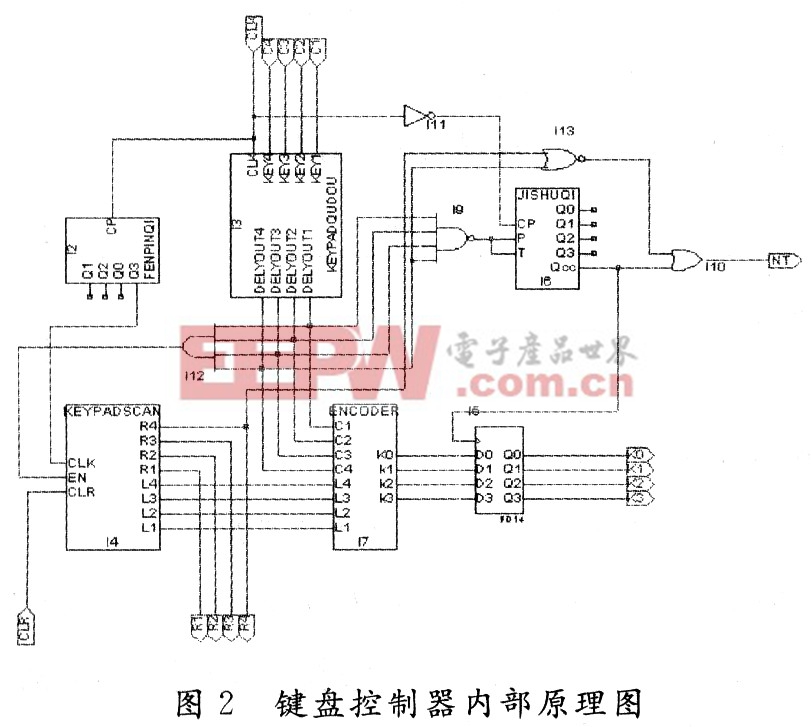

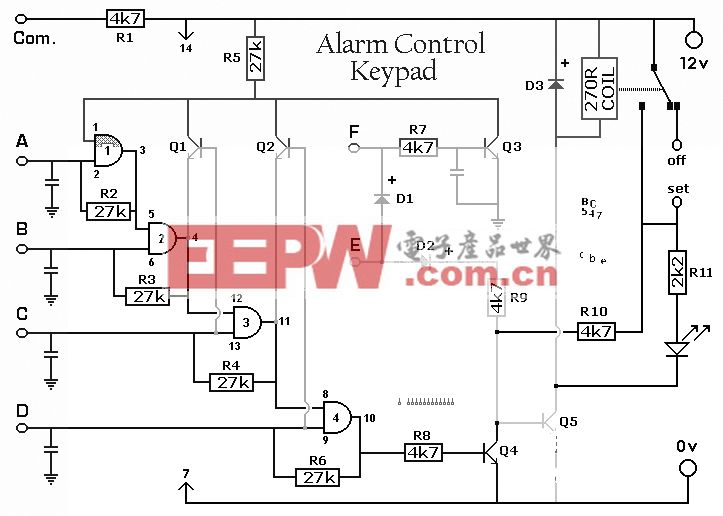

键盘控制器内部由键盘扫描电路、编码器电路、键盘去抖动电路、分频器电路、计数器电路和键值锁存器组成,如图2所示。

(1)键盘扫描电路是一个能自启动到所需要状态的状态机,当系统上电并同时输入一个有效的复位清零信号CLR后,扫描电路输出端R1~R4(L1~L4)则依次按照设计要求循环输出以下扫描电平1110,1101,1011,0111。L1~L4作为编码器的输入,通过与列回复线(C1~C4)的对应关系参与编码。然而R1~R4是将L1~L4加上高电平使能三态门输出的键盘行扫描线。将行扫描线加上三态门输出,是为了防止当一列上的2个或更多按键被同时按下时,将使LC4128V的引脚高低电平短接,如果这种情况发生,不但影响键盘控制器的准确性,更严重的是会烧坏可编程逻辑器件LC4128V,所以该控制器通过三态门输出行扫描线。三态门的使能信号就是其通过的信号取反,这样输出的高电平将为高阻状态。通过对键盘的行线分别接个上拉电阻便可得到与L1~L4一样的输出信号。

评论