PSoC3内部模拟布线和管脚选择

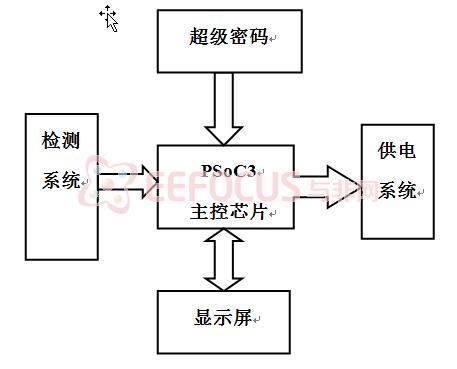

摘要:本文首先介绍了PSoC3内部的模拟总线分布,说明了PSoC Creator的模拟布线功能以及在设计中需要遵守的一些应用规则,在模拟资源使用较多或对模拟性能要求较高的应用中,设计者要遵照这些规则以达到高性能和高资源的使用。

关键词:PSoC3,模拟布线

1,PSoC3模拟总线介绍

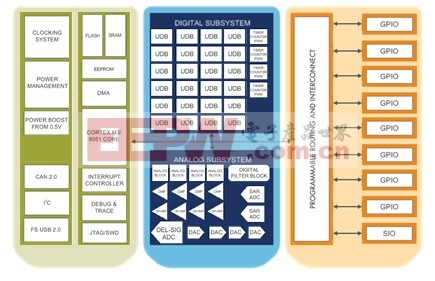

PSoC3内部可以分为模拟和数字两部分,模拟部分包括Delta-Sigma ADC、运算放大器、比较器、DAC和SC/CT模块。数字部分包括如CPU、RAM、ROM、DMA、UDBs、时钟等等。

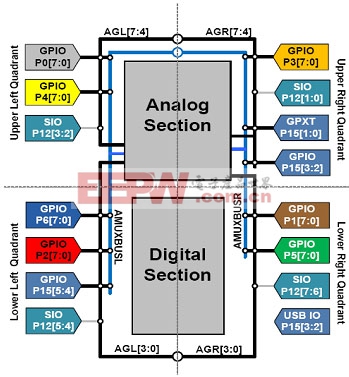

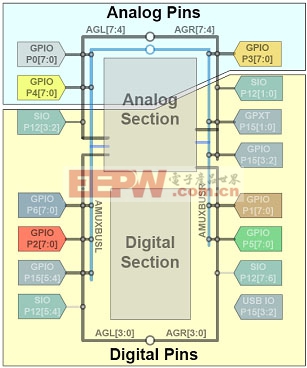

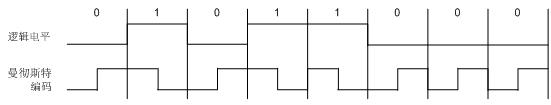

模拟全局总线(AGs)和模拟多路复用总线(AMUXBUS)提供GPIO与内部模拟模块之间的连接,如图1所示,PSoC3一共有16根AGs分别分布于4个象限,每个象限包括4根AGs总线(AGR[7:4], AGR[3:0], AGL[7:4], 和AGL[3:0]);AMUXBUS可用于任何GPIO和大部分模拟模块输入输出之间的连接。这样,AGs和AMUXBUS可在GPIO和模拟模块之间提供高达18路的信号连接。

对于内部模拟模块之间的互连,PSoC3采用模拟局部总线(ABUS)来完成,ABUS总线一共8根,其中4根ABUSL[3:0]位于芯片左边,4根ABUSR[3:0]位于芯片右边。

另外在GPIO和模拟模块之间还有大约20路的专用通道,这些专用通道可提供低阻抗连接,比如在PSoC3中的IDAC和运算放大器Opamp,后面第3部分专门介绍。

图1,PSoC3 内部模拟/数字部分分布

2,PSoC3模拟布线事例

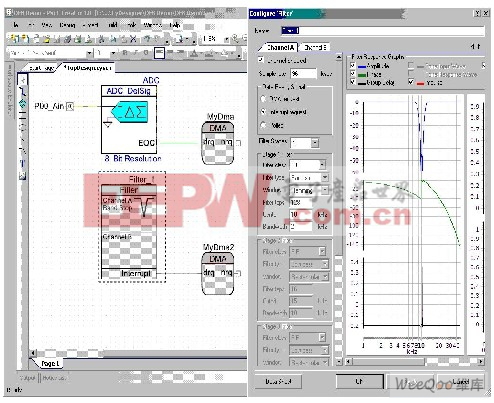

Cypress提供的软件工具PSoC Creator可为用户提供模拟布线,当然用户也可以自己手动布线模拟器件以选择更好的管脚和更优的走线,下面以一个设计事例来说明。

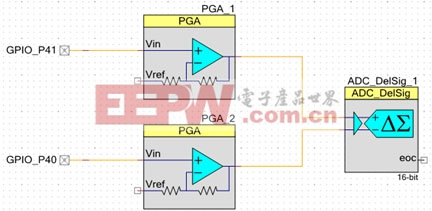

若需要信号从P4[0]和P4[1]输入,经PGA1和PGA2放大,然后接入ADC的差分输入以采集信号,其在PSoC Creator中设计的原理图如下图2所示:

图2,PSoC Creator原理图

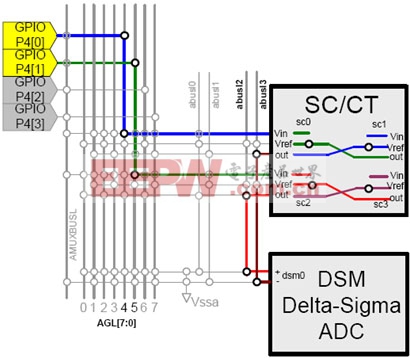

编译后,PSoC Creator自动布线,在PSoC3芯片中实际的走线如图3所示:

图3,PSoC3实际走线图

从图3可以看出,GPIO P4[0]和P4[1]是通过AGL[4]和AGL[5]连接到SC/CT模块的。而PSoC3芯片中两内部模块SC/CT和DSM ADC之间的连接是通过ABUSL1和ABUSL3实现的。

3,GPIO直接连接布线

如前所述,有些模块可以不经过AMUX/AGs或者ABUS而直接连接到指定的GPIO口上。对VIDAC而言,只有当它配置为电流数-摸转换器(IDAC)时才可以直连到GPIO口的,表1列出了每个DAC和GPIO口的对应连接。

表1,IDAC直接连接GPIO口

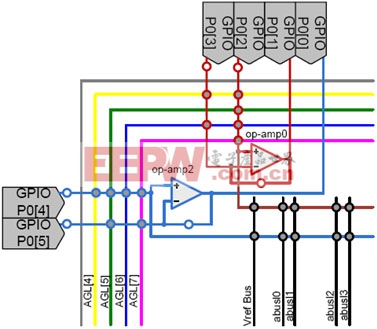

运放op-amp模块同样可直接连接到指定的GPIO上,如图4所示。表2列出了可与Opamp输入输出直接连接的GPIO口。

表2,Opamp直接连接GPIO口

图4,GPIO直接连接Opamp0和Opamp2示意图

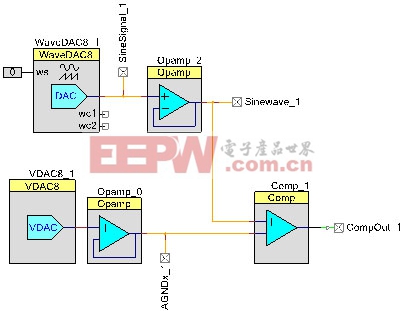

从图4可以看出,P0[1]和P0[0]是直接连接到OPamp0和OPamp2的输出,当然,你也可在PSoC Creator中设计为把OPamp2的输出连接到其它管脚上,但此时P0[0]上依然有OPamp2的输出。所以建议用指定的GPIO口与之相连。对如图5所示正弦波输出应用事例,WaveDAC8_1的作用是产生正弦波,Opamp2配置成电压跟随器模式以提高正弦波的驱动能力,VDAC8_1和Opamp_0用与提供参考电压,Comp_1是比较器。如前所述我们应将Opamp2的同向输入SineSignal_1配置为P0[4],输出Sinewave_1配置为P0[0]。

图5,正弦波输出应用事例

4,模拟管脚的最佳选择规则

PSoC3系列中管脚最多资源最丰富的封装是100Pin TQFP,它有7个完整的8-Pin I/O口,这56个 GPIO均可用做模拟信号的输入输出。端口P0、P3和P4位于芯片的上半部,并且有模拟全局总线AGL[7:4]和AGR[7:4]与之相连,对于那些低于16bit模拟性能要求的应用,任何GPIO口都可使用并且性能都一样,但对需要高性能低躁声的应用,最好选择P0、P3和P4作为其输入输出管脚。

因此,对于模拟管脚的选择,应遵守下列步骤:

1)对于给定的应用需要多少个模拟管脚I/O

2)决定哪些信号需要特定的GPIO口作为其输入输出,把这些GPIO口优先分配

3)然后依次从P0、P3和P4对其他模拟输入输出口分配管脚

4)在模拟GPIO管脚与设计所需要的其他管脚之间画条线

5)注意保持所有的模拟管脚在所画线的一侧,而所有的数字管脚在线的另一侧。

经过上述步骤就可简单的在芯片和电路板上把模拟和数字信号隔离。如下图6所示:

图6,理想的模拟数字信号隔离

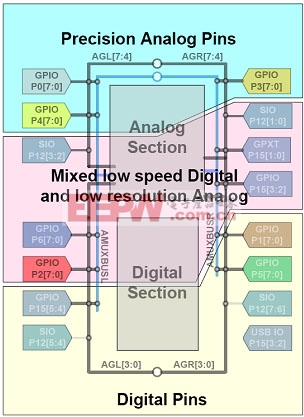

有时应用设计需要多种信号的混合,比如精确的模拟信号、低分辨率的模拟信号、低速度的数字信号和高速的数字信号,这时可以用低精度和低速的数字信号来隔离高精度的模拟信号和高速数字信号,如下图7所示。

图7,三种信号的混合分布

5,结束语

本文是对PSoC3内部模拟布线和管脚选择的一个简单介绍,对PSoC3芯片设计规定的IDAC和Opamp直接连接到GPIO做了详细的说明,但没有涉及太多太深的模拟信号知识。如果有用户觉得不够详细或者在使用PSoC3过程中碰到什么问题可参考PSoC3的技术操作手册。

评论