星载电子设备多余物数据采集系统的设计

摘要:为实现尺寸较大、内部结构较为复杂的星栽电子设备的多余物自动检测,设计了以EZ-USB FX2和CPLD芯片为核心器件的数据采集卡,实现了四通道的同步数据采集和传输。此系统包括数据采集、数据缓存以及数据控制和传输,分别采用了采样率为500 k的12位A/D转换器件AD7892、16 kx18位的FIFO CY7C4265、EPM7064和USB芯片CY7C68013。重点介绍了数据采集系统的硬件组成和软件设计,包括USB的固件程序、CPLD的控制程序和主机用户程序。实验结果表明,该系统能达到稳定传输速度为15.4 MB/s,保证了四通道同时以500 k的采样率工作的稳定性和正确性。

关键词:多余物;电子设备;USB;CPLD;CY7C68013

星载电子设备是航天电子系统中不可缺少的电气部分,直接影响着航天电子系统的可靠性。多余物是影响电子设备可靠性的主要因素之一。多余物是指在电子设备生产、制造、封装及使用过程中在其密封腔体内部残留或产生的各种金属或非金属颗粒。在航天设备工作过程中,外部冲击或振动使多余物游离随机运动碰撞,可能导致电子设备内部器件误动作或失效,甚至造成航天事故,是亟待解决的重大问题。

微粒碰撞噪声检测法(Particle Impact Noise Detection,PIND)是目前应用最为广泛的一种多余物检测方法。目前,元器件级(如继电器)的PIND方法已经被列入我国军事工业标准,对保证我国应用于航天型号中军用电子元器件有无多余物起到了重要的作用。相对于电子元器件,电子设备的尺寸更大、重量更重、内部结构更为复杂,由于电子设备和电子元器件在诸多方面的差异,使得电子元器件的PIND方法无法适用于电子设备。针对电子设备这样系统级的多余物检测方法,还没有标准可循,相关的研究还处于探索阶段。

数据采集技术是多余物检测系统中一个极为重要的信息处理环节,考虑到利用各通道数据的相关性分析,采用同步实时的多通道信号采集技术,可为自动判别多余物的存在与否提供了较为丰富的数据。数据传输给上位机有多种方式,USB支持主机与各种即插即用的外设之间进行数据传输,支持不同速率的同步和异步传输方式,理想的最高传输速率可达480 Mb/s,具有传输数率高和便携等特点。USB设备应用于数据的实时采集是非常合适的,已逐渐取代各种传统的设备(如RS232、PCI设备等),在实际中应用更加方便。目前,市场上现有的USB数据采集卡较多,但成本较高、非同步采集和传输灵活性差等缺点。

本文是在星载电子设备的多余物检测系统的需求下,依据电子设备尺寸更大、重量更重、内部结构更为复杂以及多余物信号的频率特性,设计并实现了采样速率为500 k的四通道同步实时数据连续采集系统,采用USB传输方式。

1 系统总体设计

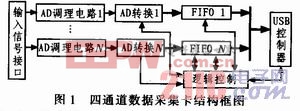

本系统是将输入的四路模拟信号通过前端的信号调理电路进行调理,再经过转换器件AD7892转换成数字信号量,经过外部FIFO(先进先出)CY7C4265的缓存,将采集到的数据有序且快速地传输至USB控制器CY7C68013,再将数据传输至上位机进行分析和处理。当上位机发出采集数据控制命令后,经CY7C68013分析,通知逻辑控制芯片EPM7064对A/D和外部FIFO进行初始化,并启动A/D开始采集数据。四通道数据采集卡结构框图如图1所示。

2 系统硬件设计

本系统硬件设计主要由数据采集模块、数据缓存模块以及数据控制和传输模块组成。

2.1 数据采集模块

前端的模拟信号量通过信号调理电路进行放大、滤波、整形,再经过电压跟随电路将信号传送至AD7892转换成数字量。AD7892是一款高速、低功耗、12位转换精度的模数转换器件,内部集成电压跟踪保持器和过电压保护电路。AD7892由外部电源系统提供5 V的采样参考电压,外部逻辑控制器件CPLD提供500 k的采样频率,可采集-5~+5 V的模拟量。由此得到可输入的最小模拟电压:1 LSB=10 V/4 096=2.44 mV。

2.2 数据缓存模块

系统为四通道连续且同步采集,每一次采集的数据量较大,而只有一个USB控制器,必须设计数据缓存模块。数据缓存芯片采用了Cypr-ess公司的16 Kx18位的FIFO CY7C4265芯片。此芯片是一款高速、低功耗CMOS时钟存储器,它的读写端口使用同步接口,每一个端口的时钟都是相互独立的,这些时钟可以是同步,也可以是异步州。这使得FIFO的读写端口能以不同的速度运行,其写时钟端口与AD7892的采样保持同步,保证了数据的不丢失。

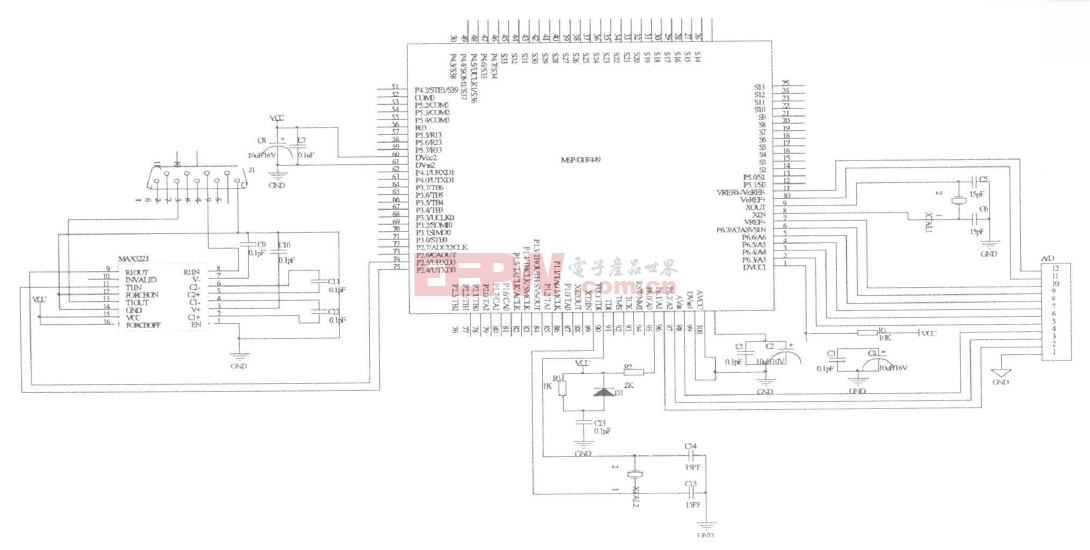

2.3 数据控制和传输模块

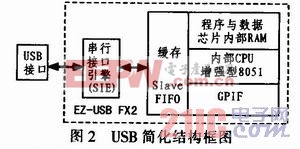

EZ—USB FX2系列芯片CY7C68013简化结构框图如图2所示。该芯片支持USB2.0规范,同时向下兼容USB1.1规范的单片机。该芯片把USB2.0收发器、串行接口引擎SIE、增强的8051内核、GPIF等集成于一体,内含4 kB的FIFO(端点缓冲区),可配置为不同大小缓冲区的IN或OUT端点(EP2、EP4、EP6、EP8),具有USB协议的4种传输方式,即控制方式、中断方式、批量方式和同步传输方式。Cypress公司为用户使用FX2提供了较为完善的软件开发工具包,降低了系统的开发难度。

FX2可配置成3种不同的接口模式,即Ports、GPIFMaster和Slave FIFO模式。在Slave FIFO模式下,FIFO[1:0]引脚作为地址线选择4个端点FIFO中的一个与FD总线连接,SLCS相当于片选信号。Slave FIFO模式又分为异步方式和同步方式的传输。在异步方式下,SLRD和SLWR是读/写选通信号;同步方式下,SLRD和SLWR作为IFCLK时钟引脚的使能信号。Slave FIFO模式是将FX2的FIFO作为外部控制器(CPLD或MCU)的从属FIFO,外部控制器可像对普通FIFO一样对FX2的FIFO进行读写。USB在传输数据时不考虑包的大小,可以明显提高效率,加快了开发的进度。本系统采用了Slave FIFO模式的异步方式进行数据传输。

评论