PSoC3应用于多通讯接口时的DMA设计

随着上层应用软件的日趋多样化,现在的便携式电子产品对嵌入式芯片的功能需求越来越高,单一或仅可以局部定制的传统芯片已经不能满足需要。因此数字系统和模拟系统都可以根据需要灵活定制成为芯片设计、开发的发展方向。Cypress为满足业界需要继PSoC1之后开发了PSoC3和PSoC5全新可编程模拟和数字嵌入式芯片。其中PSoC3使用基于单循环流水线的高性能8051内核(67MHz/33MIPS),PSoC5则是基于32位ARM Cortex-M3的内核(80MHz/100MIPS);两者都内置闪存、SRAM,支持片外存储器访问,在8、16和32bit应用中同时实现了高集成度和高灵活性。本文重点讲述了PSoC3在多通讯接口设计中的应用,以及如何使用多DMA技术提高通讯的速度和效率。

本文引用地址:https://www.eepw.com.cn/article/201706/347200.htm一、 Cypress PSoC3芯片介绍

Cypress PSoC3使用基于单循环流水线的高性能8051内核 (67MHz/33MIPS),提供业界广泛采用的5.5V至0.5V电压范围和低至200nA的休眠电流,可以满足极低功耗的应用场合。PSoC3的高性能模拟子系统和数字系统都拥有可编程通路,允许将任何模拟或数字信号(包括可编程时钟)分配到任何通用I/O引脚,这为使用者提供了真正的“系统级”可编程能力。

Cypress PSoC3的芯片编号是CY8C38xx,该系列芯片依据功能模块的不同包含多种芯片。表1是CY8C38xx系列的选型指南,除了表中列出的特性外,每个CY8C38xx芯片还包含:1.024V±0.1%的精密片上电压参考源,带PLL的1~66MHz±1%的精密可编程时钟源,有ECC(错误校正码)功能的Flash,DMA(直接存储器访问),4KB可调试跟踪的RAM,JTAG/SWD编程/调试接口,支持片外存储器访问等。

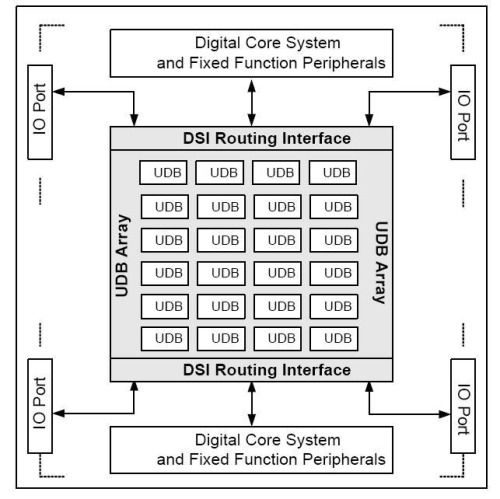

Cypress PSoC3 内部采用CPLD的结构实现了完全的数字可编程电路。图1显示了CY8C38xx系列内部的可编程逻辑图。从图1中可以看出,外设和逻辑部分可以彼此互联,也可以连接到任何引脚。数字可编程逻辑包括了以下部分。

UDB(Universal Digital Blocks)形成了可编程数字系统的核心功能,由PLD和Data path组成,可以创建各种通用外设和定制化功能。

UDB Array由多个UDB通过矩阵和可编程互联组成,支持UDB和DSI(Digital System Interconnect)之间很灵活的扩展。

DSI是数字信号的集中互联,包括UDB,固定功能外设,I/O,中断,DMA和其它部分的数字信号。

强大的模拟资源以及灵活的模拟布线资源也是PSoC3的一大亮点之一。图2是CY8C38系列芯片的片内模拟资源图,通过这些可编程的模拟电路,可以构成标准的模拟信号处理模块。并且这些模拟资源可以通过内部的模拟互连子系统进行连接,提供高度的模拟设计自由度以及IP资源的保护。模拟子系统有以下系统构成。

·有模拟全局和局部总线,模拟开关构成的高度可配置的结构。

·高精度的Delta-Sigma ADC.

·支持8位的电压或者电流DAC.

·四路比较器并且可以有选择性的互联到LUT中.

·多达四个的SC/CT模块可以构成OPAMP等模拟电路

·多达四个内部的OPAMP,可以连接到GPIO作为大电流输出的缓冲器。

·CapSense子系统支持电容触摸的检测。

·内部高精度参考电压源。

图1 CY8C38系列芯片的片内可编程数字系统图

除了模拟和数字可编程逻辑外,CY8C38 系列芯片都包含了一个专用于数字滤波的硬件加速器DFB(Digital Filter Block),它内部的专用乘法器和加速器可以在一个系统时钟内计算一个24 位数与24 位数的乘法。使用DFB 可以方便的实现FIR 和IIR 数字滤波器,而且几乎不占用MCU 的资源。在实现滤波器之外,DFB 还可以作为PSoC3 的算法加速器,可以很方便快捷的实现各种数字算法,而且不需要占用PSoC3 的CPU 资源。

评论