一种出租车计费器设计方案

引言

本文引用地址:https://www.eepw.com.cn/article/190931.htmEDA使用户在无需实际芯片、电路板和仪器仪表的情况下进行电路设计和分析;采用在系统编程技术,在现场对系统进行逻辑重构和升级,实现硬件设计软件化。

EDA技术以可编程逻辑器件FPGA和CPLD及其开发系统为硬件平台,以EDA开发软件如Max+PlusⅡ为开发工具,基于逻辑功能模块的层次化设计方法设计数字系统。Max+PlusⅡ设计可采用原理图、硬件描述语言(VHDL)等多种输入方式,并支持这些文件的任意混合设计。对于不同层次,可采用不同的输入方式进行设计。由于VHDL擅长描述模块的逻辑功能,所以在对底层模块设计中,常采用VHDL进行描述,而原理图则擅长描述模块间的连接关系,故在顶层设计中,常采用原理图输入方法。

出租车计费器一般采用以单片机为核心的设计方法,设计不够灵活方便。为此,在此介绍了采用EDA技术的层次化设计方法设计出租车计费器的方法。即用VHDL编写各个功能模块,实现低层设计;用原理图输入方式描述各模块间的关系,实现顶层设计。采用FPGA可编程逻辑器件为系统控制单元,无需添加外围电路,更新功能仅需修改软件。实验表明,该设计方法简单快捷,所设计的系统性能可靠。应用该方法设计的数字电子系统具有很强的灵活性。

1 出租车计费器功能

出租车计费器的功能要求:

(1)实现出租车按行驶里程收费,起步费为7.0元;

(2)行驶3 km后再按2元/km计费,车停时不计费;

(3)能预置起步费和每公里收费,并能模拟汽车启动、停止、车速等状态。

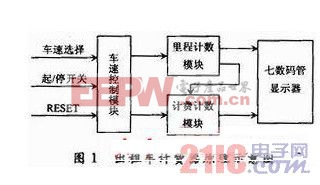

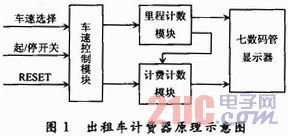

根据VHDL特点,设计者不再需要考虑选择固定功能的标准芯片,而是从实现系统功能与性能出发来,建立出租车计费器系统模块,如图1所示。

2 出租车计费器的设计与实现

本系统分底层和顶层2个层次设计,底层设计采用VHDL编写各个功能模块,顶层设计采用原理图方式描述各模块间的连接。

2.1 底层文件的设计

底层模块包括:出租车车速控制模块;计费器里程计数模块;计费器计费计数模块3个模块。

以出租车车速控制模块为例介绍。

出租车车速控制模块用于控制出租车的车速。图1中,当起/停开关及清零信号RESET都为“1”时,汽车启动就开始进入里程计数和计费器工作状态。通过改变“车速选择”端的输入值可以控制汽车行驶快慢。用CLK6作为车速控制模块的时钟输入,CLOCK6作为输出,用A、B作为车速选择变量,分别取值从“00”→“01”→“10”→“11”时,车速越来越块。其VHDL程序代码如下:

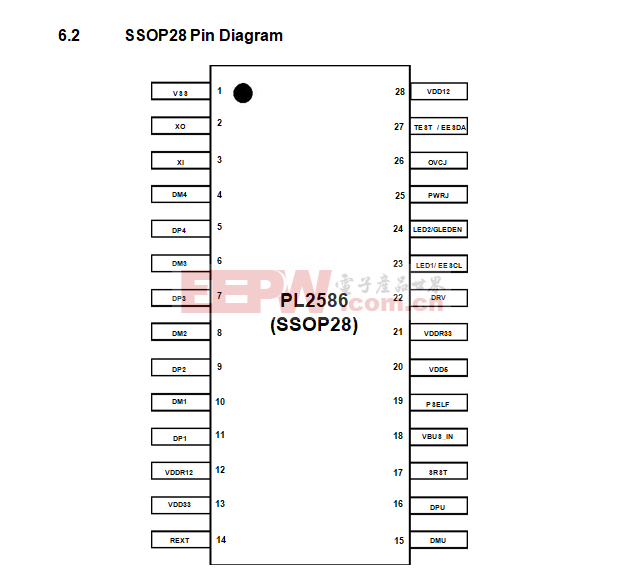

以上程序代码经过编译后生成相应模块符号,如图2所示,供顶层设计时调用。

![[组图]精密的单电源光检测电路设计方案](http://uphotos.eepw.com.cn/fetch/20220926/59_97_17_0.jpg)

评论