基于CPLD的线阵CCD驱动电路设计

摘要 论述了线阵CCD驱动电路的工作原理和现状,选择基于CPLD驱动线阵CCD工作的方案。采用MAXⅡ器件的EPM240T100C5N为控制核心,以TCD1500C为例,设计了基于CPLD的线阵CCD驱动电路,完成了硬件电路的原理图的设计,并实现了软件调试。通过QuartusⅡ软件平台,对其进行了模拟仿真。实验结果表明,设计基于CPLD的线阵CCD驱动电路能够满足CCD工作所需的驱动脉冲。

关键词 线阵CCD;复杂可编程逻辑器件;驱动时序;硬件描述语言

如何实现高精度的运动装置角度和位移测量,一直是系统或设备设计中需要解决的关键技术之一。随着半导体微电子技术的迅猛发展,各种新型器件不断涌现,其中线阵CCD(Charge Coupled Devices)电荷耦合器件因其所具有的高精度、无接触、高可靠性等优点,应用越来越广泛。

1 总体方案设计

线阵CCD一般不能直接在测量装置中使用,因此CCD驱动信号的产生及输出信号的处理是设计高精度、高可靠性和高性价比线阵CCD驱动模块的关键。

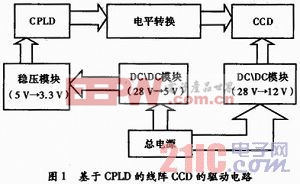

传统驱动CCD的设计方法使CCD的工作频率较慢,信号输出噪声增大,不利于提高信噪比,不能应用于要求快速测量的场合。而用可编程逻辑器件CPLD进行驱动,则可提高脉冲信号相位关系的精度,以及提供给CCD驱动脉冲信号的频率,而且调试容易、灵活性高。目前,在工业技术中,多采用基于CPLD的驱动电路实现线阵CCD的驱动。系统框图如图1所示。

2 硬件设计

2.1 CPLD的硬件电路的设计

以CPLD(Complex Programmable Logic Device)器件为核心,设计线阵CCD的驱动电路。然后在其基础上扩展,选择其他元器件,设计出与其相配套的电路部分,经调试后组成硬件系统。

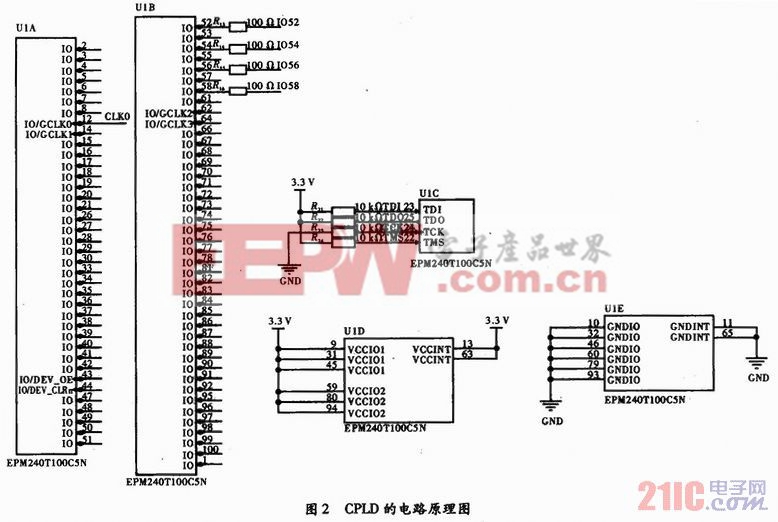

CPLD的电路由5部分组成,有源晶振向EPM240T100CSN的U1A的IO/GCLK0口输入时钟脉冲CLK0,提供了CPLD工作的时钟脉冲,因为时序逻辑的需要。U1C从JTAG端口中下载程序,U1B的52、54、56、58口输出脉冲信号。U1D管脚接3. V电压,U1E管脚接地。电路原理如图2所示。

评论