基于SOPC的PCI总线高速数据传输系统设计

摘要:本文针对一体化侦察通信接收机高速数据传输的需求,提出了一种基于SOPC实现PCI总线高速传输系统的设计方案。该方案将PCI桥与用户逻辑集成到一片FPGA上,并利用片上CPU实现了DMA控制器的自动配置和总线异常处理,提高了系统数据速率。经硬件平台验证,该设计能够实现大于100M bytes/s的PCI总线传输速率。

关键字:PCI总线;现场可编程门阵列;片上系统;直接存储器存储

随着战场电磁环境复杂程度越来越高,侦察与通信系统的融合成为一种必然的发展趋势。数据量大、算法复杂是数字化侦察接收系统的主要特征。使用DSP和FPGA进行高速信号谱分析、滤波等预处理,借助通用计算机平台实现信号的分选、显示等后处理是一种理想的系统设计方案。因此,如何构建与PC机间的高速数据通道,便成了侦察接收系统设计中的关键问题之一。PCI (Peripheral Component Interconnect)总线,即外围部件互连总线,是目前应用最广泛的一种高速同步总线,在32位总线宽度33Mz时钟下,其理论最大传输速率可达132Mbyte/s (64位总线宽度66MHz时可达到528Mbyte/s),因此成为上述侦察接收系统中高传输速率、低成本PC接口的首选实现方式。目前,实现PCI总线接口的常用方法有两种:一是采用专门的PCI桥芯片实现PCI接口,如PLX公司的PCI905X系列芯片等;二是使用可编程芯片实现PCI接口。

随着集成电路技术的发展,可编程芯片成本越来越低、资源越来越丰富,用户可将PCI桥和其它用户逻辑在一片可编程芯片上实现,其中后者不需要额外的PCI桥芯片,系统硬件电路得以简化,系统的稳定性和可靠性更高,进而可以缩短系统开发周期。基于以上考虑,本文提出一种采用可编程片上系统(System-On-Programmable-Chip,SOPC)实现侦察接收机PCI总线高速数据传输系统的设计方案,并采用直接存储器访问(Direct Memory Access,DMA)传输方式来提高数据传输速率。

1 PCI总线接口方案设计

在PCI总线接口标准中,根据数据传输的发起者所在位置,PCI接口有从模式和主模式两种工作模式。根据工作方式的不同,DMA传输方式可分为连续式DMA (Continuous DMA)和集散式DMA(Scatter-Gather DMA)两种。

1.1 PCI模式的选择

PCI总线标准中,由PC发起数据传输、读/写PCI接口卡的模式称为从模式。这种模式只要求PCI接口设备具备PCI从设备的功能,接口逻辑相对较简单;主模式是由PCI接口卡主动读写PC内存,PCI接口的逻辑相对复杂。频繁地要求PC发起数据传输会占用PC的资源,为了减少PC的负担,使其有更多的资源用于后续的数字信号处理,在侦察接收系统中,PCI接口卡的传输模式选择主传输模式。

1.2 DMA传输方式的选择

DMA是提高数据传输速率和微处理器使用效率的一种数据传输机制。连续式DMA用于实现连续数据块的传输,即在一次DMA传输中设备端读/写物理地址连续变化(读存储器空间)或不变化(读IO口),PC端的物理存储地址连续变化。集散式DMA用于实现不连续数据块的传输,各传输数据块的起始读/写地址和长度都可以不同,它采用一个寄存器链表存储每个数据块的读/写起始地址和长度,DMA传输过程中自动从该链表加载地址和长度信息。集散模式DMA应用灵活,其缺点是在传输完一个数据块之后要重新配置DMA控制寄存器的值,速度比连续模式稍慢。在侦察接收系统中,DMA传输模式选择连续式传输模式。

1.3 PCI总线DMA传输方案设计

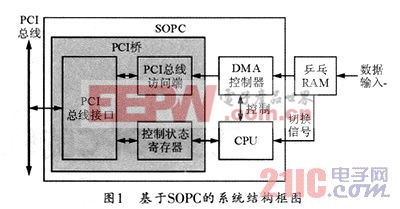

PCI接口总体结构框图如图1所示。数据输入到乒乓RAM缓冲区,乒乓切换信号通知CPU数据准备好,CPU通过PCI桥的控制状态寄存器判断PC端是否备妥,如PC备妥则配置并启动DMA控制器,DMA控制器读口从乒乓RAM中读数据,写口将数据写至PCI总线访问端,PCI总线接口单元申请并获得PCI总线访问权,将数据送上PCI总线。

2 PCI总线接口的SOPC实现

SOPC是Ahera公司提出的一种灵活、高效的片上系统解决方案,它将处理器、存储器、I/O口以及一些通用的功能模块集成在一个PLD器件上,构成一个可编程的片上系统。利用SOPC开发侦察接收机中的PCI总线接口,具有开发周期短、系统稳定性好的优点。

评论