Vivado HLS把ELS带入主流

可能Vivado设计套件采用的众多新技术中,最具有前瞻性的要数新的VivadoHLS(高层次综合)技术,这是赛灵思2010年收购AutoESL后获得的。在收购这项业界最佳技术之前,赛灵思对商用ESL解决方案进行了广泛评估。市场调研公司BDTI的研究结果帮助赛灵思做出了收购决策(见赛灵思中国通讯杂志第36期“BDTI研究认证以DSP为核心的FPGA设计的高层次综合流程”http://china.xilinx.com/china/xcell/xl36/2-7.pdf)。

本文引用地址:https://www.eepw.com.cn/article/190470.htmFeist表示:“VivadoHLS全面覆盖C、C++、SystemC,能够进行浮点运算和任意精度浮点运算。这意味着只要用户愿意,可以在算法开发环境而不是典型的硬件开发环境中使用该工具。这样做的优点在于在这个层面开发的算法的验证速度比在RTL级有数量级的提高。这就是说,既可以让算法提速,又可以探索算法的可行性,并且能够在架构级实现吞吐量、时延和功耗的权衡取舍。”

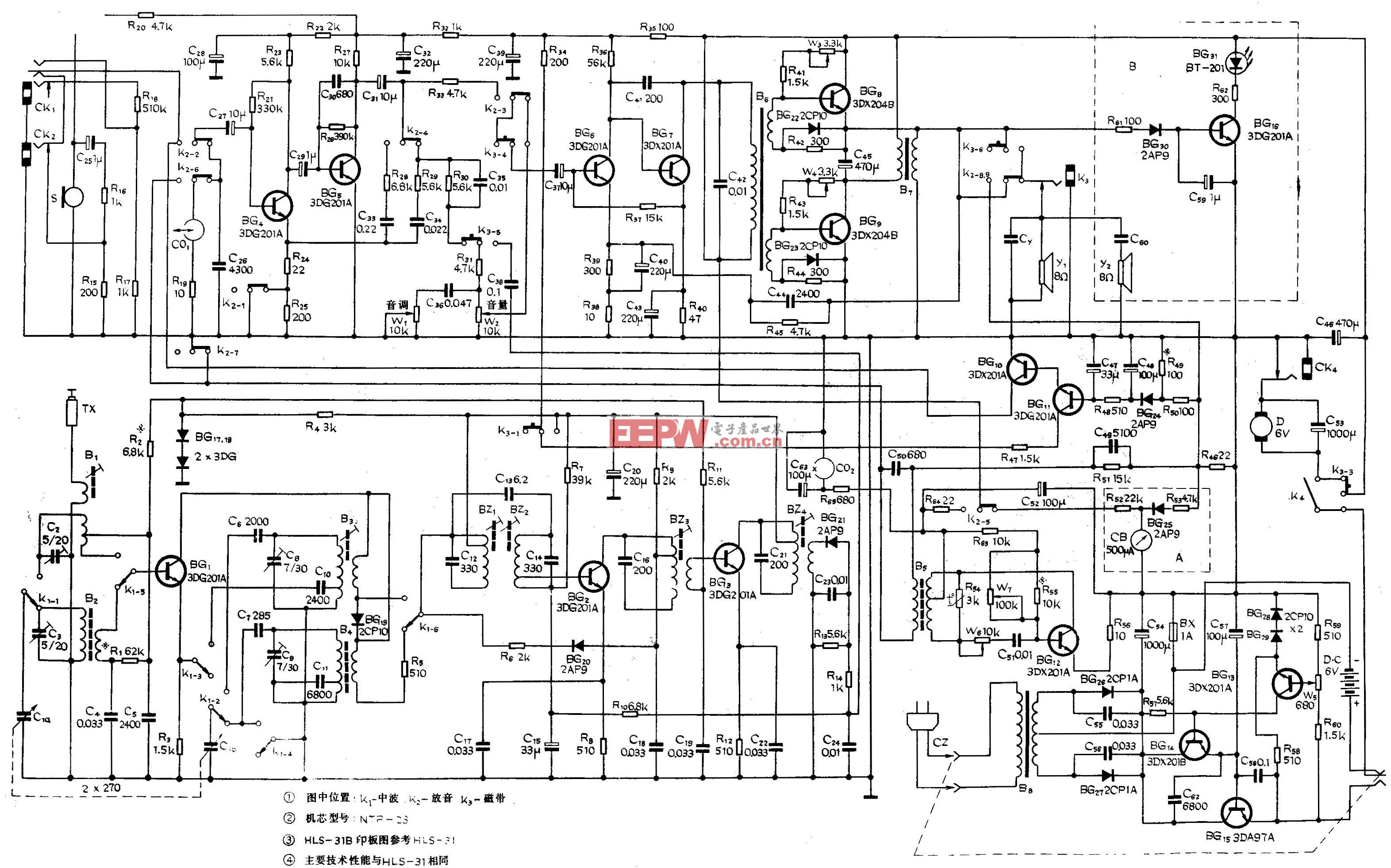

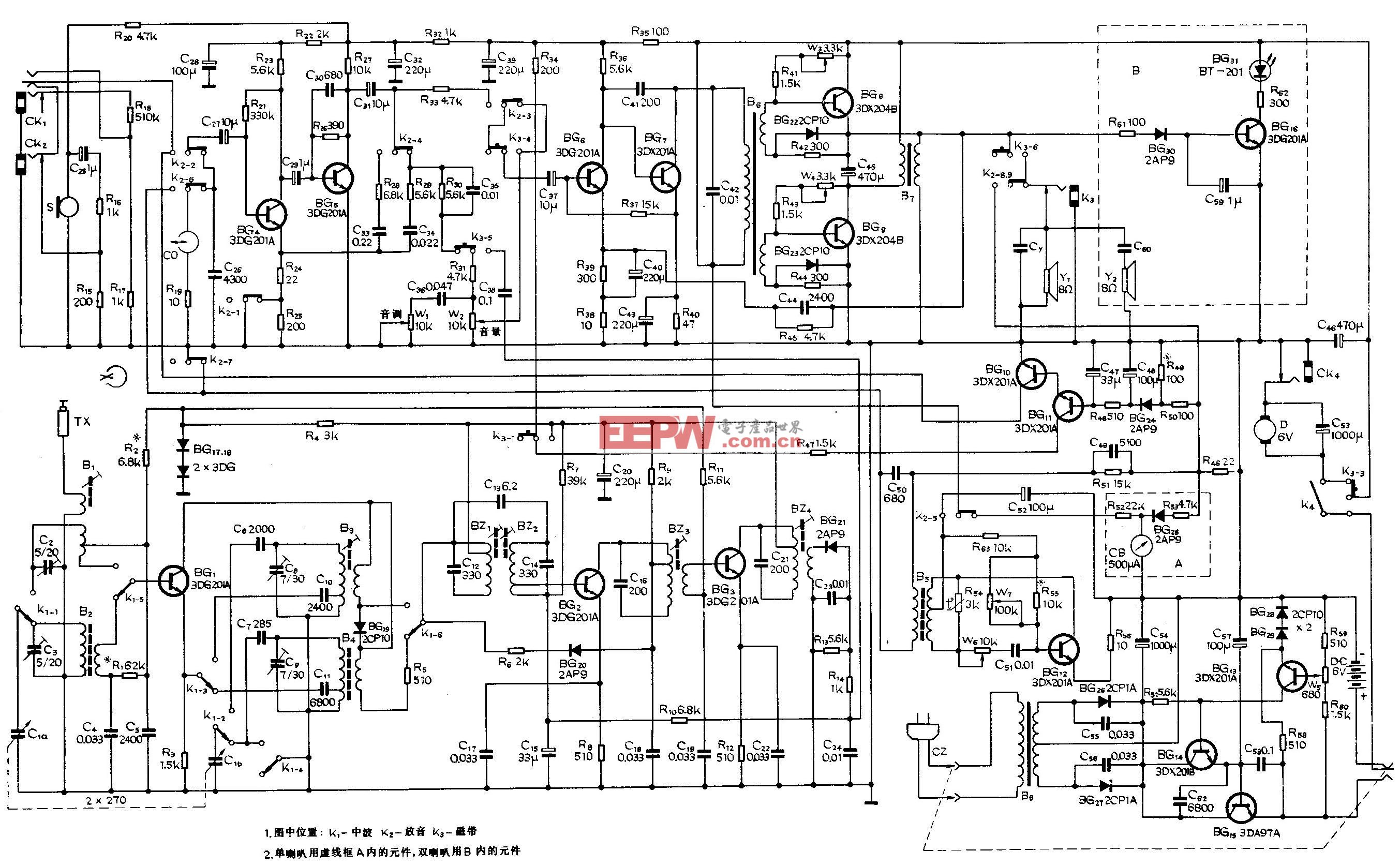

设计人员使用VivadoHLS工具可以通过各种方式执行各种功能。为了演示方便,Feist讲解了用户如何通过一个通用的流程进行VivadoHLS开发IP并将其集成到自己的设计当中。

在这个流程中,用户先创建一个设计C、C++或SystemC表达式,以及一个用于描述期望的设计行为的C测试平台。随后用GCC/G++或VisualC++仿真器验证设计的系统行为。一旦行为设计运行良好,对应的测试台的问题全部解决,就可以通过VivadoHLSSynthesis运行设计,生成RTL设计,代码可以是Verilog,也可以是VHDL。有了RTL后,随即可以执行设计的Verilog或VHDL仿真,或使用工具的C封装器技术创建SystemC版本。然后可以进行SystemC架构级仿真,进一步根据之前创建的C测试平台,验证设计的架构行为和功能。

设计固化后,就可以通过Vivado设计套件的物理实现流程来运行设计,将设计编程到器件上,在硬件中运行和/或使用IP封装器将设计转为可重用的IP。随后使用IP集成器将IP集成到设计中,或在系统生成器(SystemGenerator)中运行IP。

评论