Board从入门到精通系列(七)

本文将给出通过Vivado IDE开发Zynq平台上PS裸机应用程序的流程。读者将看到Vivado开发更高效、快捷。

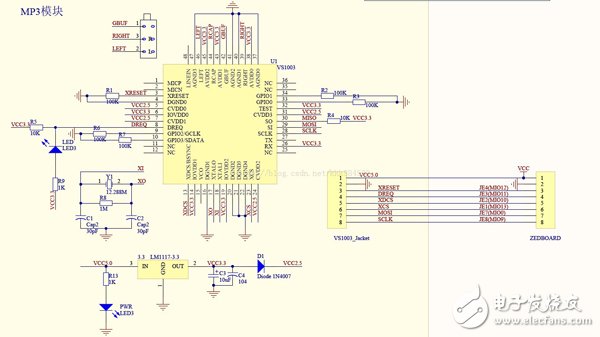

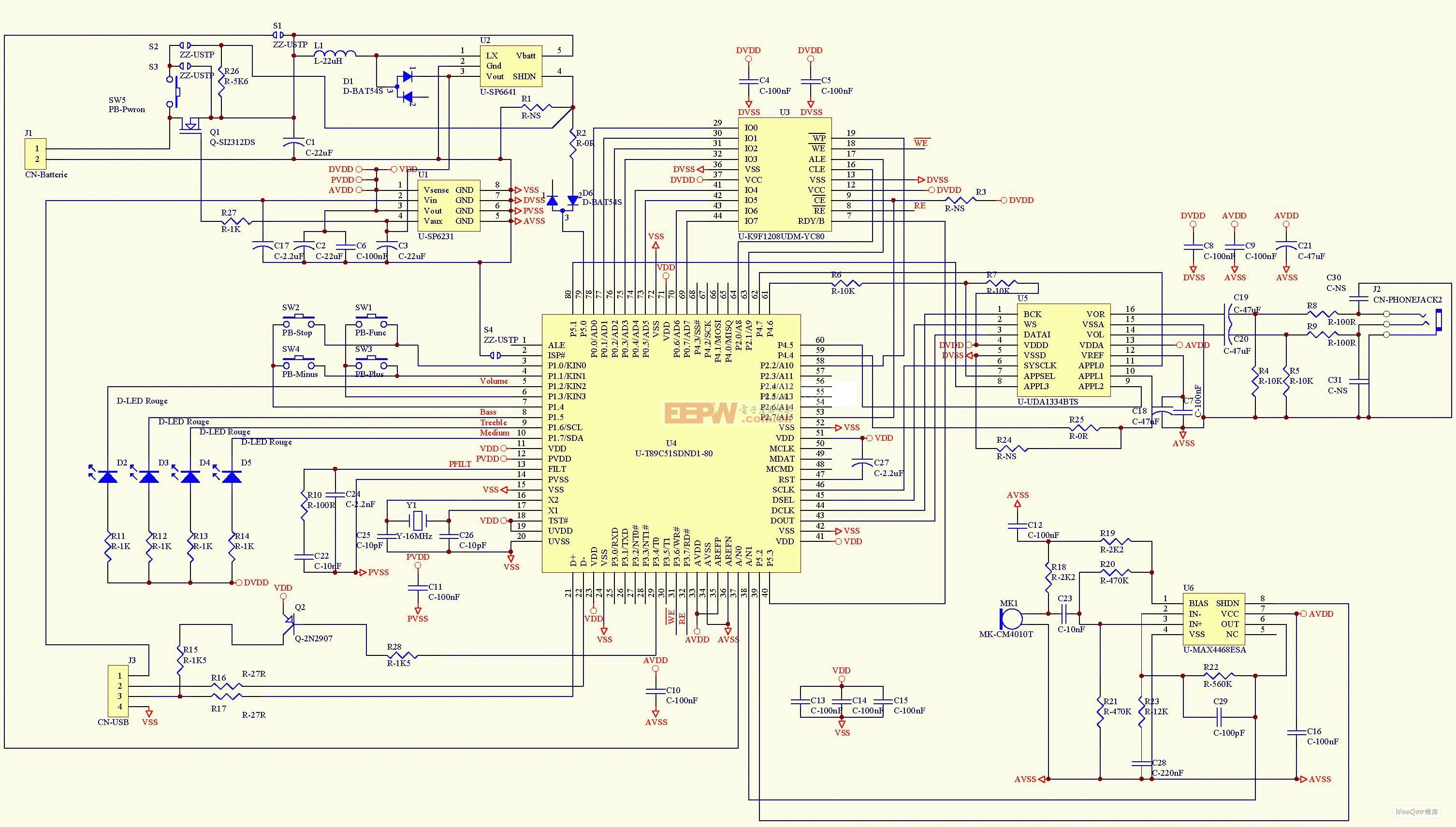

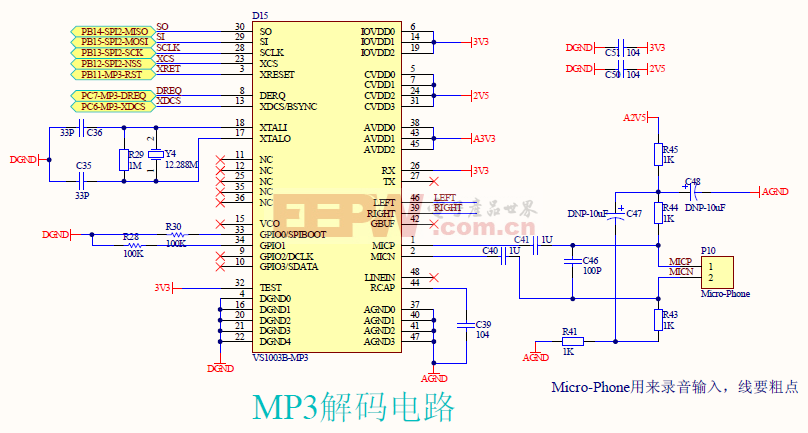

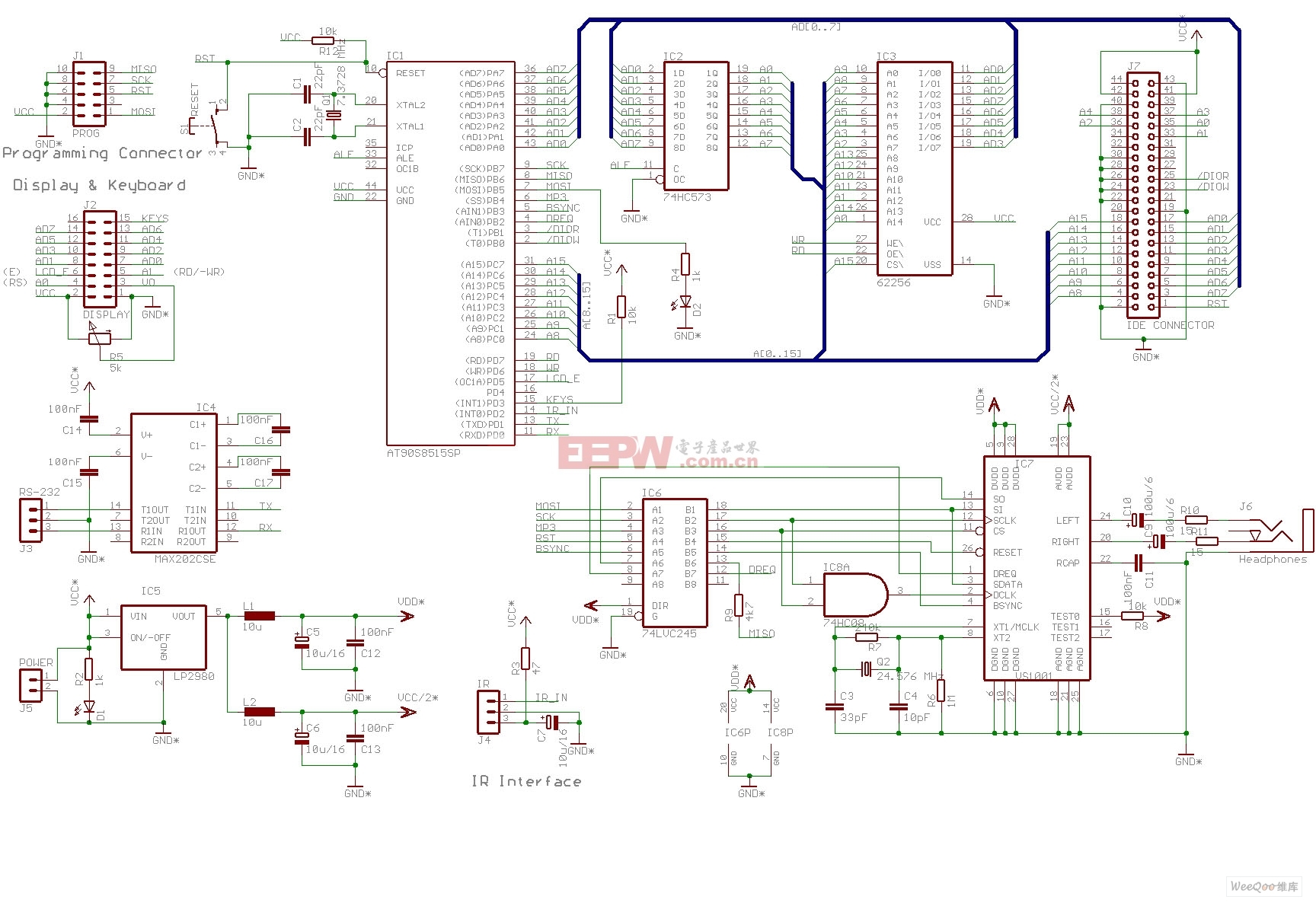

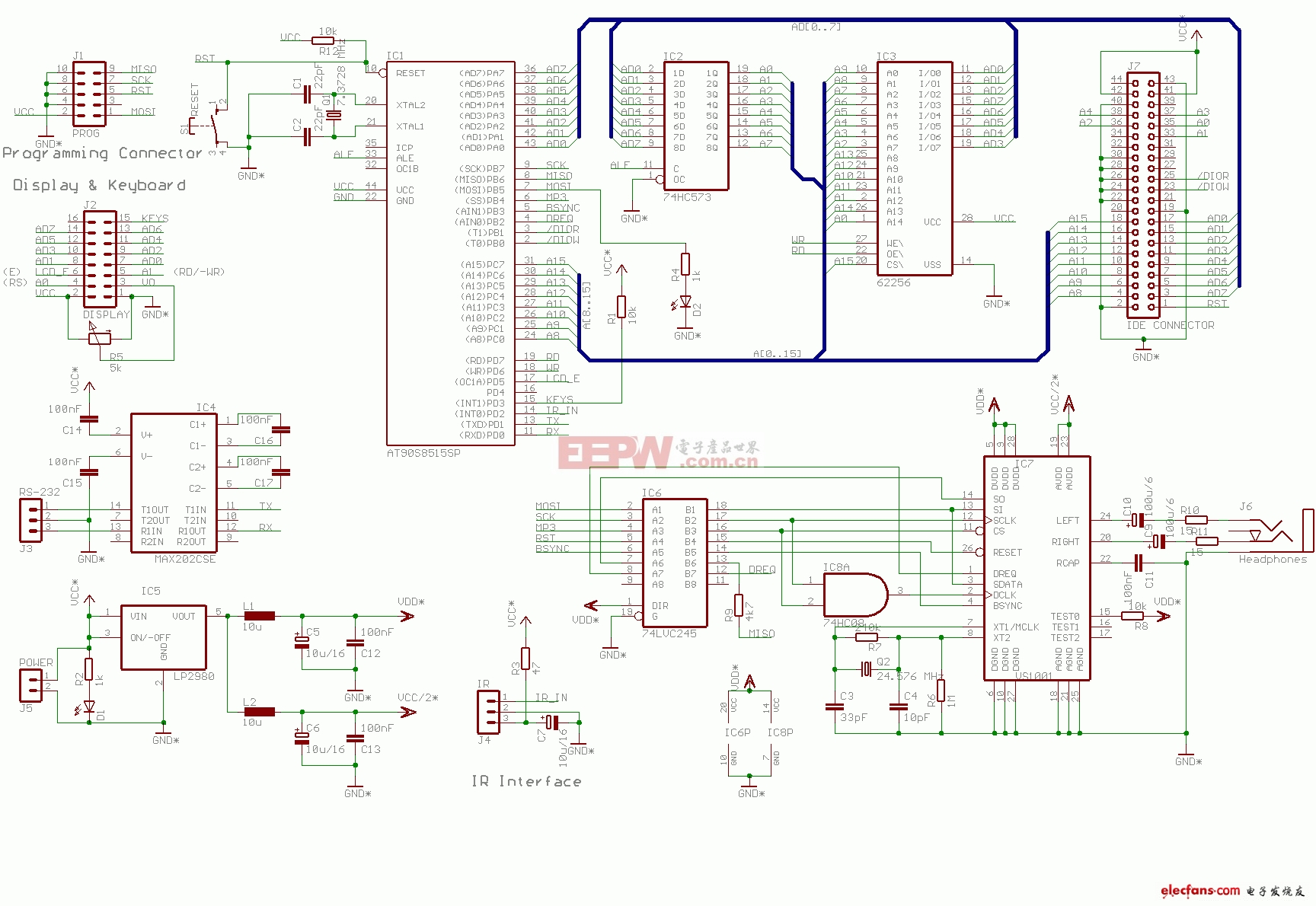

本文引用地址:https://www.eepw.com.cn/article/201710/365594.htmMP3我们都听过,现在我们可以用ZED-Board来听。板子上有音频芯片ADAU1761,可以实现录音、放音,但不具有MP3解码功能。Zynq 双核ARM9做MP3软件解码应该是可以实现的,但是博主本人有一颗VS1003,可以实现MP3硬件解码,软件将得以简化,对MP3解码原理感兴趣的可以深入研究如何利用CortexA9+ADAU1761实现MP3播放。电路图如下:

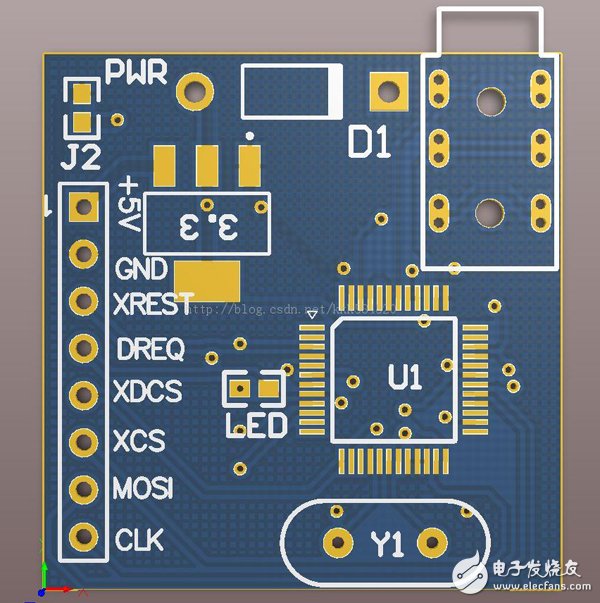

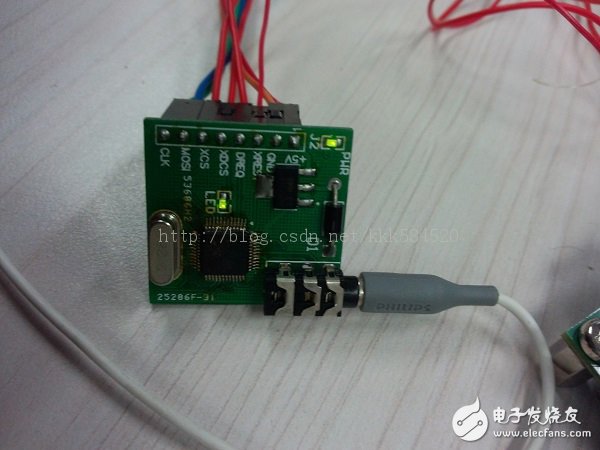

利用Zynq MIO实现VS1003控制,这样只和PS有关,PL完全可以丢弃。在本节基础上,读者可以尝试将SPI模块移到PL上实现,这样可以降低PS部分IO读写频率,提高CPU利用率。实物连接图如下:

Zynq板子外接用排母,为了使用杜邦线,需要一个双公排针,可以用普通单排2.54mm排针压制而成

下面介绍软件开发流程。建立Vivado工程,命名为MP3Player,过程遵循上节Vivado建立工程步骤,略。

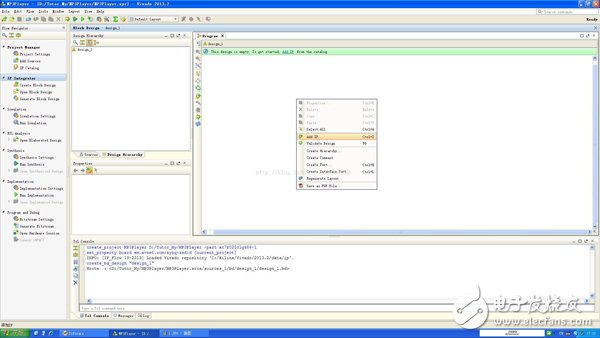

进入IDE后,点击左侧流程管理器中的IPI Integrator下的Create Block Design。 这个工具是2013.1版本后才出现的,将取代XPS完成系统集成。

在编辑区右键,选择Add IP...,名称保持默认design_1.bd

搜索框中输入zynq,双击第一个,添加IP到电路图中。

添加完成后,自动进行布线连接,点下图中圆圈区域 Run Block AutomaTIon。

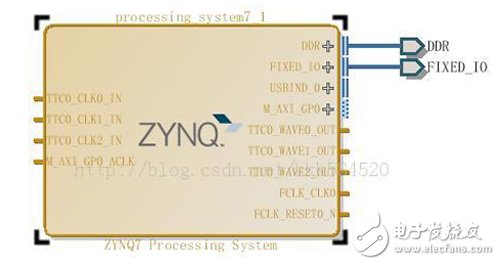

等待完成,结果如下图所示。

可以看到,DDR和固定IO自动进行了连接。这是因为我们建立工程时选择了ZedBoard DVK,这样就能按照板子描述自动连接引脚到相应外设。

另外看到,默认状态下使能了M_AXI_GP0,可以将PL部分带AXI从接口的IP连接到PS进行控制。本节不需要,所以必须禁用,否则验证设计时会报错。双击方块,见下图

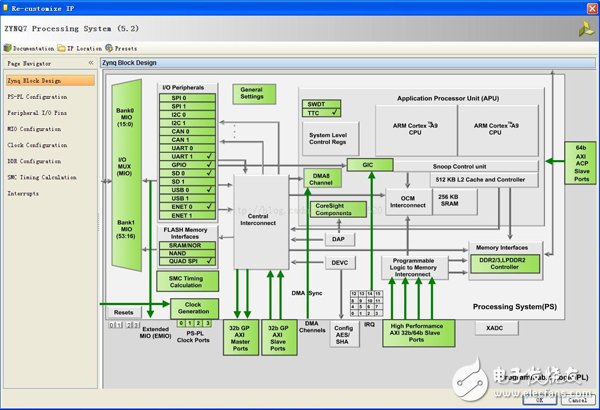

看到了熟悉又陌生的画面,有些像XPS中Zynq视图,但精简了很多。单击左侧“PS-PL ConfiguraTIon,界面如下:

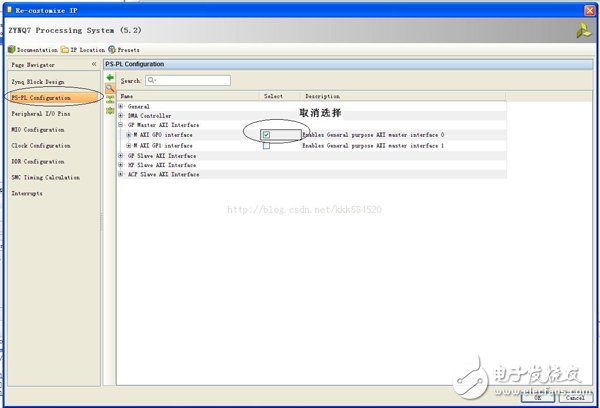

将AXI GP0接口后的勾取消选择,确认,回到IPI。

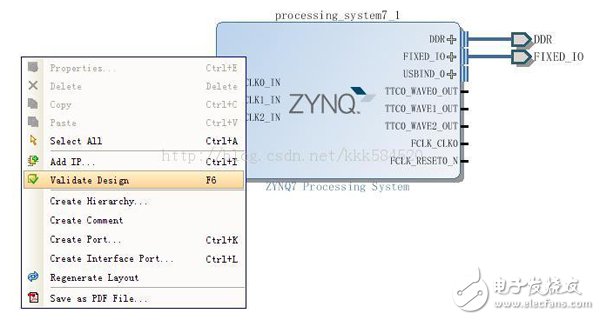

验证设计,在空白处右键,点击Validate Design。无误,点确认即可。

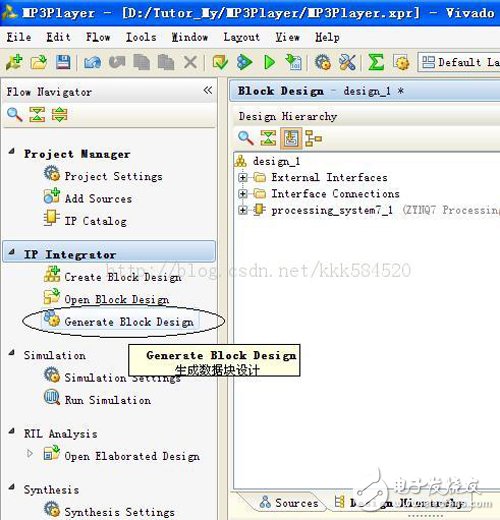

在上图位置点Generate Block Design,确认。

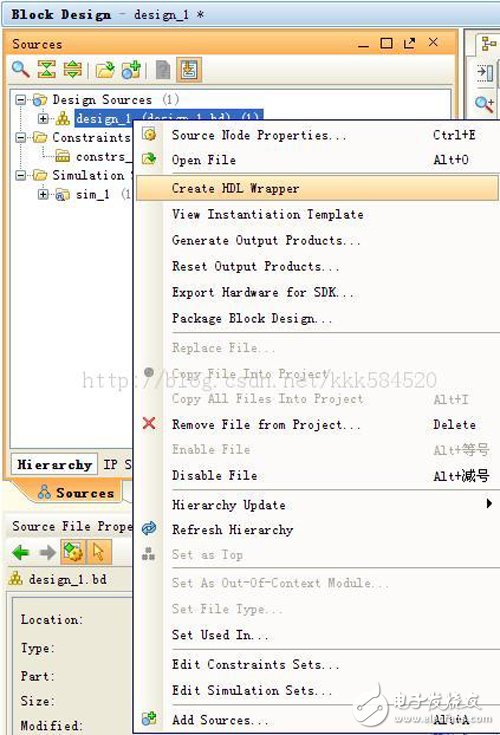

在Sources窗口中找到design_1,右键选择生成顶层HDL包装。确认。

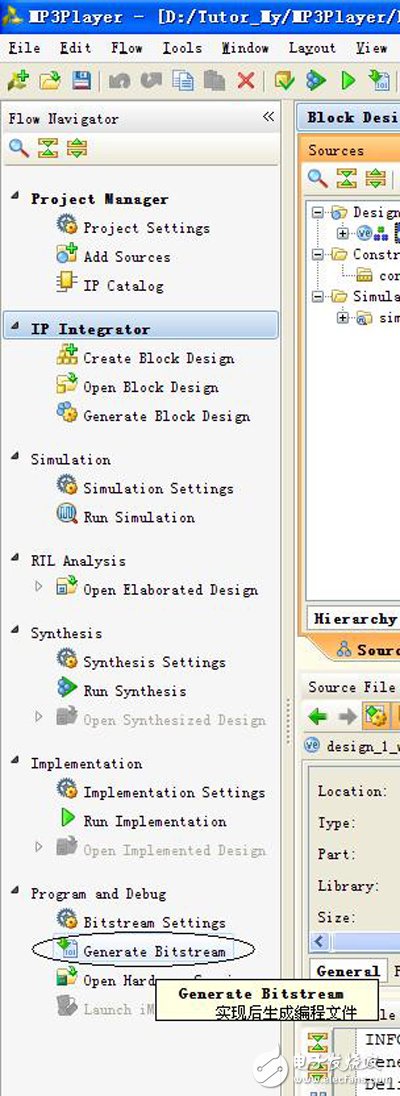

直接点左侧流程中的Generate Bitstream,一步到位。完成比特流大约需要5~8min。

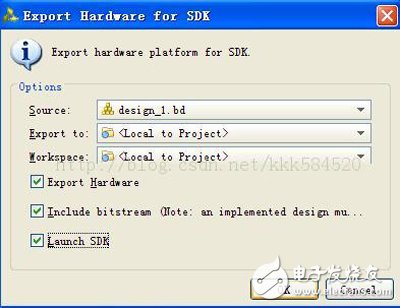

完成后,先Open Implementated Design,再导出到SDK。

完成后,先Open Implementated Design,再导出到SDK。如果没有做这一步,上图中第二项会变成灰色。

后面就是SDK开发了,和本系列教程(三)中相同。建立ApplicaTIon工程,C工程,模板helloworld。将代码改为下面:

#include

#include platform.h

#define MIO_BASE 0xE000A000

#define DATA0 0x40

#define DATA0_RO 0x60

#define DIRM_0 0x204

#define OEN_0 0x208

void delay(unsigned int t)

{

unsigned int i,j;

for(j=0;j

评论