Board从入门到精通系列(七)-本文将给出通过Vivado IDE开发Zynq平台上PS裸机应用程序的流程。读者将看到Vivado开发更高效、快捷。

关键字:

MP3 Board Vivado

使用VIVADO对7系列FPGA的高效设计心得-随着xilinx公司进入20nm工艺,以堆叠的方式在可编程领域一路高歌猛进,与其配套的EDA工具——新一代高端FPGA设计软件VIVADO也备受关注和饱受争议。

关键字:

FPGA VIVADO 赛灵思

Board从入门到精通系列(六)-由于更新了开发工具,所以本篇博客有必要重复前面的内容,今天首先演示如何利用Vivado开发纯逻辑工程,即只在PL上进行开发。

关键字:

FPGA Vivado OpenRISC

All Programmable技术和器件的全球领先企业赛灵思公司(Xilinx, Inc.)宣布,在今天发布的Vivado® Design Suite HLx 2017.1版中广泛纳入部分重配置技术,为有线和无线网络、测试测量、航空航天与军用、汽车以及数据中心等丰富应用,提供动态的现场升级优势和更高的系统集成度。 动态现场升级 利用赛灵思部分重配置技术,设计人员能夠即时变更器件的功能,无需全部重配置或重建链接,从而大幅提高了All&nb

关键字:

Xilinx Vivado

用于共享工具命令语言脚本的开源库已发布在GitHub.com上。在过去五年里,赛灵思把战略重点放在设计方法和工具上,通过提供业界最先进、最全面的开发环境,解决生产力问题,加快设计周期,促使产品更快上市。即便新一

关键字:

TCL Vivado UltraFast

在编写软件时,您有没有遇到过无论怎么努力编码,软件都不能按您期望的速度运行?我遇到过。您有没有想过,“有没有什么简单而且成本不高的方法可将一些代码输入多个定制处理器或定制硬件?”毕竟,您的应用

关键字:

FPGA Vivado

您的开发团队是否需要在极短的时间内打造出既复杂又富有竞争力的新一代系统?赛灵思All Programmable器件可助您一臂之力,它相对传统可编程逻辑和I/O,新增了软件可编程ARM处理系统、可编程模拟混合信号(AMS)子系统

关键字:

Vivado 设计套件 SoC

本文将介绍如何优化赛灵思内核以便在CPRI远程无线电头端设计中使用Vivado IPI。新型基于FPGA的设计使用IP核的数量和种类日趋繁多。Vivadoreg;设计套件中的IP集成器 (IPI) 工具和赛灵思通信IP让设计人员能够更加轻松

关键字:

Vivado

通过用于重构高级算法描述的简单流程,就可以利用高层次综合功能生成更高效的处理流水线。如果您正在努力开发计算内核,而且采用常规内存访问模式,并且循环迭代间的并行性比较容易提取,这时,Vivado设计套件高层次

关键字:

算法重构 Vivado 赛灵思

时钟扩展对使用赛灵思Vivado设计套件的工程师来说是一个很大的挑战,但不是一个不可逾越的障碍。随着越来越多的赛灵思用户开始使用Vivadoreg;设计套件,部分用户对未扩展时钟表示困惑。那么什么是未扩展时钟呢?他们

关键字:

时钟扩展 Vivado

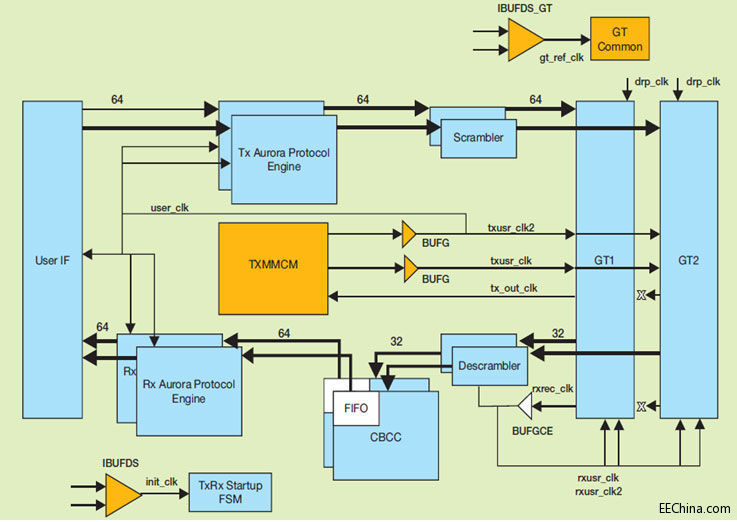

赛灵思的 IP Integrator 工具可帮助您改善设计输入生产力和多核 Aurora 设计的资源优化。 作者: K Krishna Deepak 赛灵思高级设计工程师 kde@xilinx.com Dinesh Kumar 赛灵思高级工程经理 dineshk@xilinx.com Jayaram PVSS 赛灵思高级工程经理 jayaram@xilinx.com Ketan M

关键字:

Vivado Aurora

All Programmable 技术和器件的全球领先企业赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布,Vivado®设计套件开始支持包括Zynq® UltraScale+和Kintex® UltraScale+器件在内的16nm UltraScale™+产品组合的早期试用。该Vivado早期试用版工具已与UltraScale+ ASIC级可编程逻辑进行了协同优化,能够充分发挥量产级UltraScale+器件的优势,进而利用整个目录中的

关键字:

Xilinx Vivado

1 提高抽象层次

Vivado HLS能提高系统设计的抽象层次,为设计人员带来切实的帮助。Vivado HLS通过下面两种方法提高抽象层次:

● 使用C/C++作为编程语言,充分利用该语言中提供的高级结构;

● 提供更多数据原语,便于设计人员使用基础硬件构建块(位向量、队列等)。

与使用RTL相比,这两大特性有助于设计人员使用Vivado HLS更轻松地解决常见的协议系统设计难题。最终简化系统汇编,简化FIFO和存储器访问,实现控制流程的抽象。HLS的另一大优势是便于架构研究和

关键字:

Vivado FIFO 存储器 RAM C/C++

接上篇

4 设置简单系统

协议处理一般情况下属于状态事务。必须先顺序读取在多个时钟周期内进入总线的数据包字,然后根据数据包的某些字段决定进一步操作。通常应对这种处理的方法是使用状态机,对数据包进行迭代运算,完成必要的处理。例3是一种简单的状态机,用于根据上一级的输入丢弃或转发数据包。该函数接收三个参数:一个是通过“inData”流接收到的输入分组数据;一个是通过“validBuffer”流显示数据包是否有效的1位旗标;第三个是称为&ldquo

关键字:

Vivado FIFO 存储器 RAM C/C++

vivado介绍

Vivado

Vivado设计套件,是FPGA厂商赛灵思公司2012年发布的集成设计环境。包括高度集成的设计环境和新一代从系统到IC级的工具,这些均建立在共享的可扩展数据模型和通用调试环境基础上。集成的设计环境——Vivado设计套件包括高度集成的设计环境和新一代从系统到IC级的工具,这些均建立在共享的可扩展数据模型和通用调试环境基础上。这也是一个基于AMBAAXI4互联规范、IP-XA [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473