一种高速缓存方案的实现方法

摘要:基于Altera公司的EP2SGX90FF1508C3N和NEC公司的UPD44165364AF5,提出了一种高速缓存方案。本设计采用可编程逻辑器件,灵活性高,可靠性强,可以根据用户的需要进行方便的扩展和升级。深入研究了QDRII SRAM的工作原理和时序原理,提出了比较可靠的读写状态机实现方案。硬件设计经过实际测试,达到了预期的指标,实现了43.2 Gb/s的数据吞吐速率,并且成功用于某产品中。

关键词:QDRII SRAM;高速缓存;时序图;状态机;FPGA

引言

在移动通信领域随着3G时代的到来和4G的发展,无线基站离不开高速率、高带宽和大动态的数据采集,采集下来的高速数据需要进行高速缓存、高速数据处理和传输。本文实现了一种基于FPGA和QDRII SDRAM高速缓存解决方案,并且经过实际验证,已成功应用于某产品中。

1 QDRII工作原理

QDR协议由存储器供应商Cypress、IDT、NEC、Renesas和Samsung公司组成的联盟共同发布,主要针对网络交换机、路由器和其他通信设备的应用。QDRII由两个独立的“读”和“写”端口组成,“读”和“写”端口有分别独立的数据输出和数据输入端口来支持相应的读写操作,并且读写端口分别为双倍数据速率端口。

QDRII SRAM提供了2字突发和4字突发结构。2字突发结构的DDR地址总线在前半个时钟周期允许读请求,后半个周期允许写请求。4字突发结构针对每一个读或写请求传输4个字,这样只需一个SDR的地址总线就能最大程度地利用数据带宽。以Cypress公司生产的CY7C1310V18为例,说明QDRII器件内部逻辑结构,如图1所示。

决定。

的上升沿第二个数据字被锁存。第三个和第四个数据字在K、控制时,在时钟K的上升沿,当读选通信号为低电平时,读地址SA被锁存。在其之后的第二个时钟K的上升沿,设备锁存Q上的第一个数据字,在接下来的的上升沿锁存Q上第二个数据字。在之后的K、的上升沿锁存Q上的第三个和第4个数据字。读总线数据输出Q值在DDR模式下从存储器中输出时,与CQ、源同步时钟边沿对齐,此时完成一个完整的读操作。

2 QDRII SRAM读写状态机

在实际的应用系统中,为了让器件连续有效地工作,必须设计相应的控制程序来完成各种控制状态之间的转换,对于4字节突发QDRII器件,设计的读写状态机如图4所示。使QDRII在读写状态中自由跳转。

选通脉冲。读/写状态机持续监控用户接口FIFO状态信号,以确定是否存在待处理读/写请求。连续不断地并发读/写请求流将导致状态机只在读状态和写状态之间转换,以确保正确无误地将请求交替发送到外部存储器。一串只写请求将导致空闲状态和写状态轮流出现,同样,一串读请求也会在空闲状态和读状态问转换。

3 系统的硬件实现

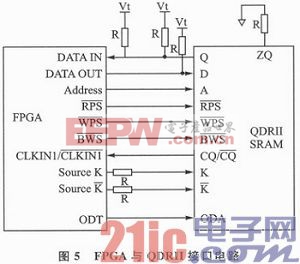

本文实现的高速缓存系统是以FPGA和QDRII器件为核心的,FPGA采用Altera公司的Stratix II GX系列,具体型号为EP2SGX90FF1508C3N Stratix II系列芯片采用90 nm工艺,1.2 V内核电压供电,具有片上可编程电阻特性,简化了设计,容易实现阻抗匹配,提高了信号完整

性。QDRII采用NEC公司的UPD44165364AF5-E33EQ2-A,具有4字节突发结构,最高工作频率为300 MHz。FPGA与QDRII的接口如图5所示。

QDRII的控制时序十分复杂,为简化设计过程,增强系统的可靠性,可以采用IP核进行控制。IP核是一种预定义的并经过验证的复杂功能模块,可以方便地集成到系统中。

Altera公司的QDRII SDRAM Controller MegaCore可提供一些底层的时序控制,使得对QDRII的控制变得相对简单,IP核留给用户一些上层的Avalon通信接口,用户可以根据自己的需要对相应的状态引脚进行监控和编写驱动,实现对QDRII器件的操作。

4 实验设计及测试结果

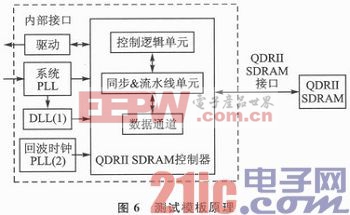

用VHDL编写testbench,测试系统性能,设计原理如图6所示。设计数据源对QDRII进行写操作,再把读出来的数据与原始数据对比,最后给出测试结果。

进行速度测试,以300 MHz的速率进行读写,通过测试证明本系统能够稳定工作,测试结果如图7所示。

为了便于观察,选取几个固定地址,循环读取该地址的数据,用SignalTap对其进行实时采样,结果如图8所示。可以清晰地看出给定固定地址00004H后,发出读请求,在avl_data_read_valid有效时读取数据为AAAAFFFFAAAAFFFFAAH,与写入数据一致。

结语

本文通过深入分析QDRII的结构和工作原理,设计一种状态机,给出了一种基于FPGA的高速缓存方案。经过实验验证,QDRII可以稳定工作在300 MHz,使36位存储器接口的总流量达到43.2 Gb/s,具有实际应用价值,使各种数据密集型应用中的读/写能力得以提升。

交换机相关文章:交换机工作原理

评论