Hummingbird加密算法的硬件架构设计

摘要 Hummingbird加密算法是针对RFID标签等硬件受限系统的轻型加密算法。其已在不同平台上得到了验证。文中提出了一种针对Humming bird算法的硬件架构,与目前其他方法相比,在响应时间基本相同的情况下,该硬件架构所需的硬件资源更少。其采用Xilinx的低端Spart an-3系列FPGA芯片作为验证平台。实验结果表明,该硬件架构可较好地嵌入到硬件受限系统中,尤其是嵌入式系统。

关键词 Hummingbird加密算法;FPGA;硬件实现

目前大多低配置的设备中均涉及到信息的传递,例如:智能卡、RFID标签等。若这些信息被非授权用户获取将带来安全威胁。因此研究可嵌入此设备中的加密算法是必要的。当前有多种加密标准算法,例如DES、AES等,但这些算法通常需要大量的硬件资源来实现,同时响应时间较长,并不适合资源受限的系统。

在众多加密算法中,Hummingbird加密算法是Revere Security开发的一种轻型算法。由于其所需的硬件资源少、功耗低,被广泛应用于一些硬件资源受限的应用场合,例如:RFID和简易嵌入式系统等。Hummingbird加密算法易于软件实现,在不同的嵌入式平台中均有相应的实现和优化方案。

目前有多种不同的硬件架构被提出,以便使Hummingbird加密算法能适用于多种硬件资源受限的平台。但这些方法所使用的硬件资源同样较多,且加密速度较慢。针对这些问题,文中在基于FPGA硬件平台下,提出了一种Hummingbird加密算法的硬件架构。在响应时间基本相同的情况下,该硬件架构所占用的硬件资源相比其他的解决方案较少。

1 Hummingbird加密算法简介

Hummingbird加密算法结合了基于块和流的加密。整个加密过程包含两部分:初始化过程和加密/解密过程。在Hummingbird算法中,使用16 bit的块长度、256 bit的密钥长度和80 bit的内部状态寄存器。

1.1 初始化过程

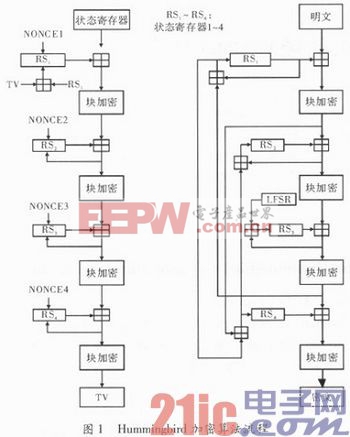

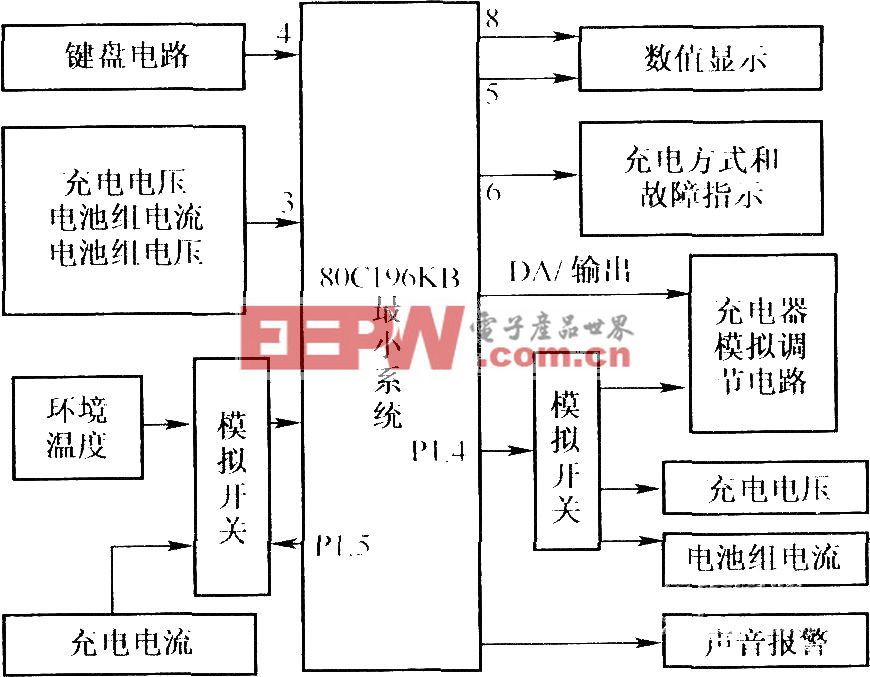

Hummingbird算法的初始化过程包括,初始化4个内部状态寄存器,同时计算LFSR的初始值。4个状态寄存器RS1~RS4首先由16 bit的随机数产生器产生。初始化过程中,4个状态寄存器经过4次的更新过程,而同时更新的结果则作为LFSR的初始值。初始化过程的流程如图1(a)所示。

1.2 加密解密过程

在初始化过程后,明文首先与状态寄存器RS1进行模216的加运算,然后再进行块加密。在加密过程中,这些操作重复进行4轮,并得到最终的密文。其中,对应的4个状态寄存器也要经过相应的更新,同样LFSR也进行更新。整个加密过程如图1(b)所示。解密过程可参照加密过程的逆运算。

评论