随钻测井系统井下传感嚣的低功耗设计

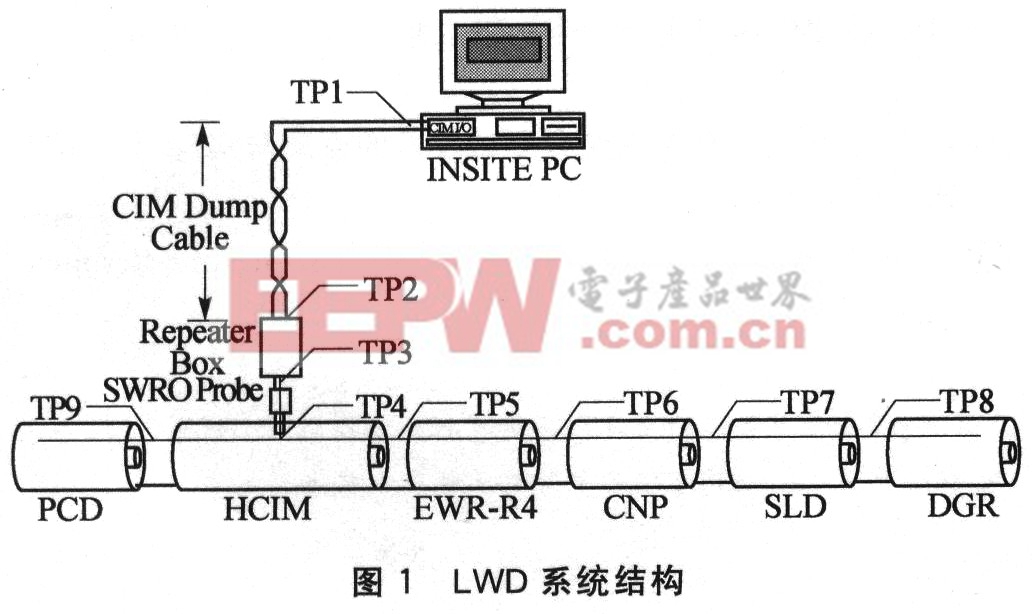

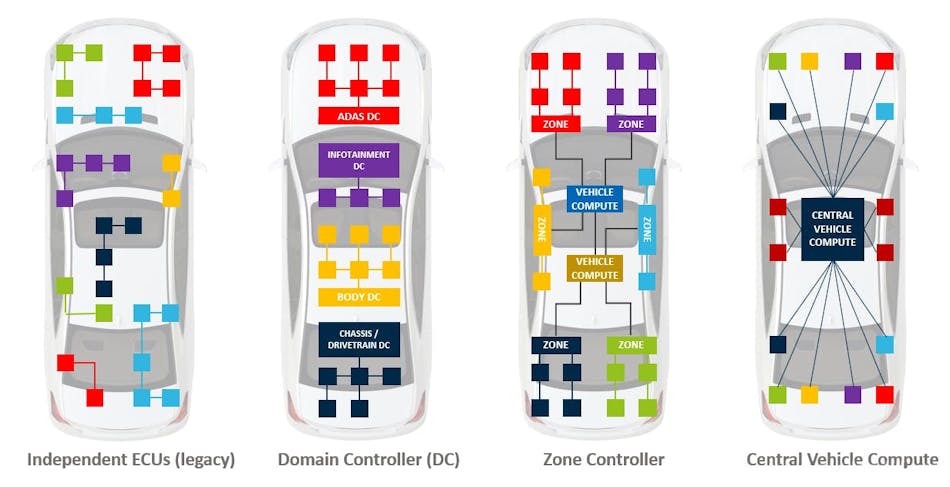

随钻测井LWD(Logging WhiIe Drilling)技术是将测井仪器安装在靠近钻头的部位,在地层刚钻开后就测量地层各种信息的一种测井方法。它通过测量地层倾角和方位、钻头方向、钻压、扭矩等,进行钻井定向控制,测量地层的电阻率、自然电位、自然伽马、密度/中子、核磁、声波时差等。LWD在钻井的过程中测量地层岩石物理参数,并用数据遥测系统将测量结果实时送到地面进行处理,形成地层评价。由于当前数据传输技术的限制,大量的数据仍存储在井下仪器的存储器中,起钻后回放。其测量结果克服了井眼扩径、泥浆入侵等一系列环境条件的影响。随钻测井可实时提供地层和井深信息,对地层做出快速评价,优化井眼轨迹和地质目标,指导钻进。特别是在疑难井、大斜度井、水平井中,它显示出比电缆测井更为重要的作用。LWD系统主要由2部分组成:地面系统和井下系统。如图1所示。

地面系统包括:上位机PC、接口卡、专用电缆、增效箱以及其他附属配件。其中主机装有LWD系统专用地质导向钻井配套软件Insite。

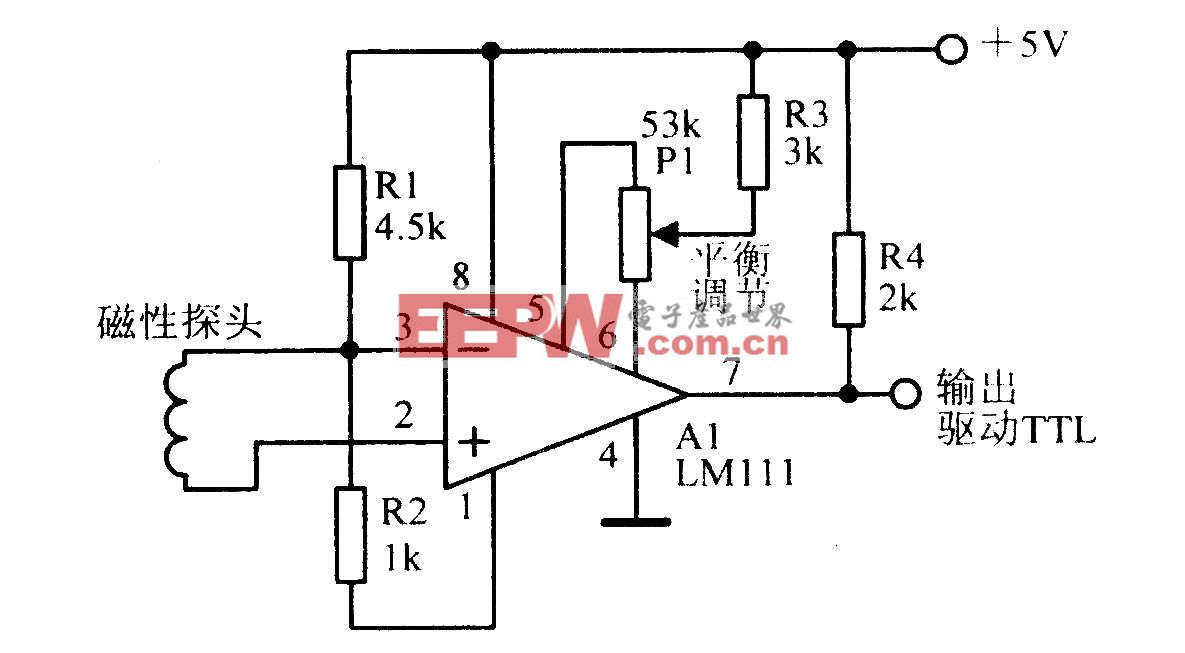

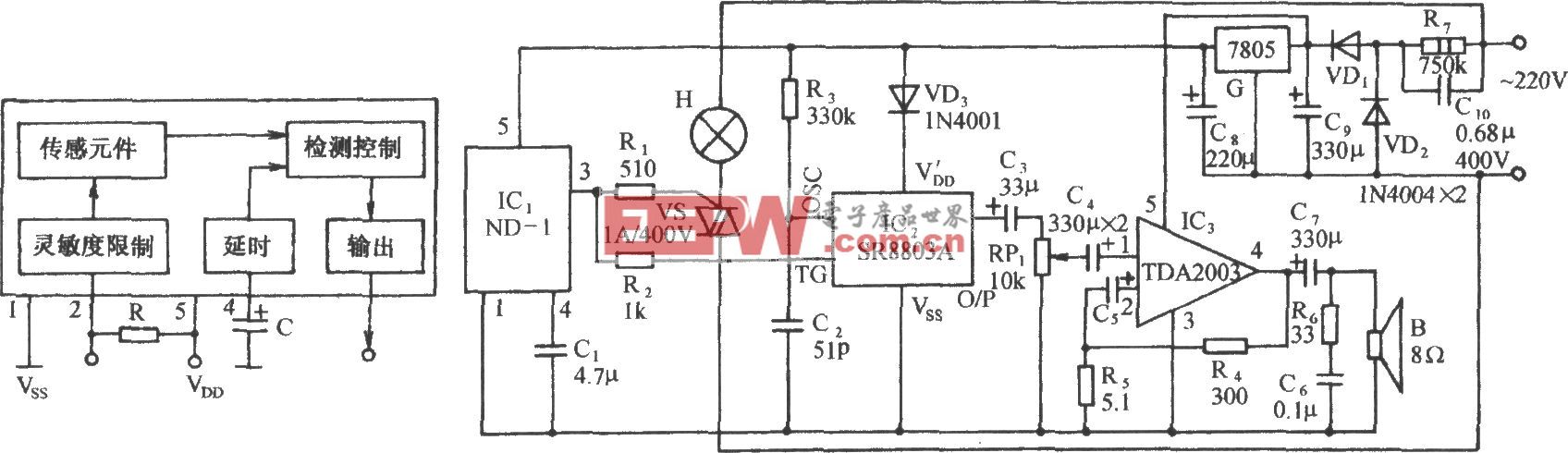

井下系统包括:总线控制器(HCIM)、随钻自然伽马测量仪(DGR)、随钻电阻率测量仪(EWR)、随钻中子传感器(CNP)、随钻岩石密度传感器(SLD)、工具串振动传感器(DDS)、探管(PCD)。

由此可见,LWD井下系统有大量传感器对不同参数进行测量,耗电量非常大。由于每次钻井设备下井都要耗费大量人力物力,而且一旦下井,钻井设备会在地下持续长时间工作,而且钻井深度可达几千米,只能通过安装在钻头附近的电池供电。随钻测井系统的供电由2组锂电池(3.6 V)并联组成,每组6节串联,构成21 V直流电源。电池储能是有一定限制的。例如渤海油田的B20井就是应用LWD技术,测量井段为2 102~3 073 km,连续工作5天。其他应用LWD钻井技术的石油井也是如此,有些LWD传感器甚至要连续在井下工作半个月之久。因此降低系统功耗就是随钻测井系统设计时需要考虑的一个十分重要的问题。

1 低功耗电路设计的基本原则

对于典型系统而言,其功耗大致满足:P=C×V2×f。C是电容负载,V是电源电压,f是开关频率。功耗与工作电压的平方成正比,因此工作电压对系统的功耗影响最大,其次是工作频率。电容负载也会有一些影响,但电容负载对设计人员而言一般是不可控的。因此设计低功耗系统,应该考虑在不影响系统性能前提下,尽可能地降低工作电压和使用低频率的时钟。

对于随钻测井系统,由于传感器在地下几千米工作,温度极高,工作空间狭小,在设计上就提出了其他一些挑战。在高温下,电容等器件的性能会减半,因此在进行器件选型时,这些因素都考虑其中。

另外,动态功耗管理也是降低功耗的有效途径。动态功耗管理是当前最重要的系统功耗优化技术之一。它根据系统各模块性能,动态地配置系统,使系统中各功能模块处于满足性能需求所需的最低功耗状态,从而实现节省功耗的目的。

2 基于MC9S12Q128的低功耗系统设计

MC9S12系列单片机是以CPU12内核为核心的16位单片机,简称S12系列。典型的S12总线速度为8 MHz,最高可达25 MHz。其I/O和CPU可以运行在不同的时钟下。CPU功耗可以通过开关状态寄存器的控制位来控制。MC9S12Q128外部采用5 V电压供电,正常运行时最大电流为5 mA,低功耗模式下不到1 mA,为设计低功耗系统提供了有利的条件。

2.1 电 源

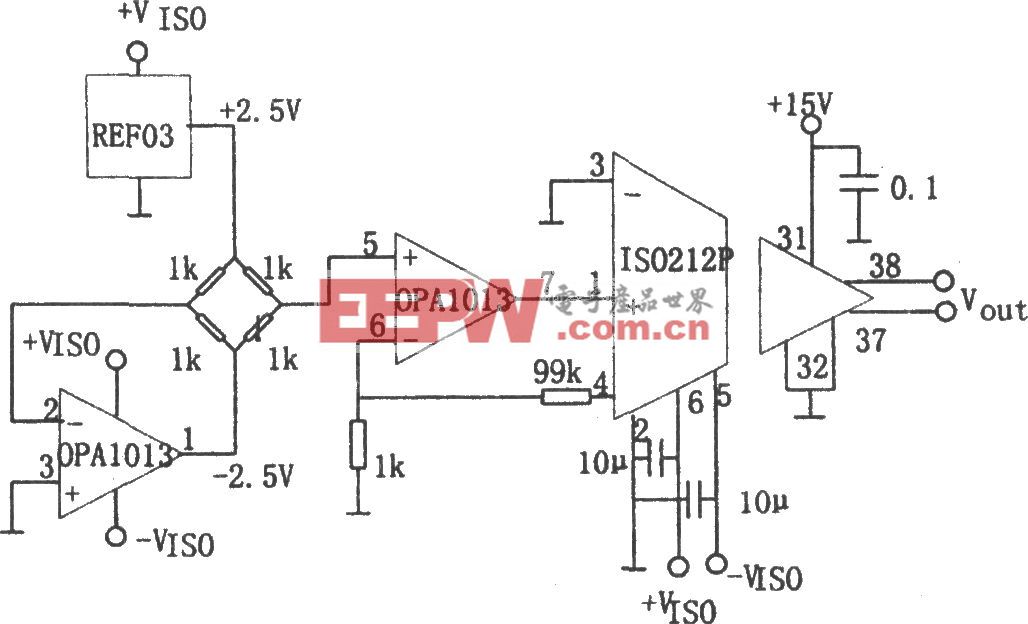

对于MC9S12Q128而言,它的外部供电电压是5 V,I/O端口也是按5 V供电的逻辑电平设计的,这样可以在使用时接口电路直接与TTL标准电平的器件连接。这些接口电路应该也是低功耗的,否则会造成一方面使用低电压降低了功耗,另一个方面使用额外的接口电路又增加了系统的功耗。芯片内部用2.5 V供电,低电压供电保证了芯片的低功耗。芯片内部5 V到2.5 V通过内部电压调整模块自行进行转换。

由于传感器系统是由电池供电,实际电池具有以下非线性特性:

①输出电压在放电过程中逐渐下降,低于某个阈值电压时,电池耗尽而停止工作;

②电池的有效能量与放电电流情况有关;

③电池具有自恢复效应,即电池在非供电时期可以回收部分电荷,从而增加了其有效量。

根据电池的以上特性,提出了根据电池状态调度任务的策略;对多电池驱动的设备,提出了以下各种电池调度和管理技术:

◆静态调度。按照一定的次序轮流使用各个电池,每个电池工作的时间固定。

◆动态调度。通过检测电池的输出电压或放电电流,确定电池的状态,从而决定各电池间的切换时间和顺序。

2.2 时钟频率

从低功耗的角度看,需要较低的频率;但是在实时应用中为了快速响应外部事件,又需要比较快的系统时钟。MC9S12Q128内部总线速率最高可达25 MHz,即40 ns的最小指令周期。MC9S12Q128内部集成了完整的节能振荡电路。如果外接振荡电路,需要配置时钟合成寄存器(SYNR)和时钟分频寄存器(REFDV)。靠锁相环产生的时钟频率由下面的公式得到:

PLLCLK=2×OSCCLK×(SYNR+1)/(REFDV+1)其中OSCCLK为外部晶振频率。

经测试,应用锁相环电路时,在21 V电压供电情况下,电流会增大5 mA左右。本设计选用16 MHz的外部晶振,总线频率为默认的8 MHz。在保证不影响系统性能的前提下,减少系统功耗。

2.3 低功耗软件控制

MC9S12Q128的工作模式通过模块的智能化运行管理和CPU的状态组合,以先进的方式支持超低功耗的各种要求。MC9S12Q128支持3种低功耗模式――停止模式、伪停止模式和等待模式。CPU条件码寄存器CCR中的S位是STOP指令禁止位,如果要进入STOP模式,该位应置0。

评论