基于压控振荡器(VCO)的高性能锁相环(PLL)设计

简介

“锁相环”(PLL)是现代通信系统的基本构建模块。PLL通常用在无线电接收机或发射机中,主要提供“本振”(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数(A/D)转换的时钟源。

随着集成电路加工中功能器件的尺寸缩小,器件电源电压也呈下降趋势,包括PLL和其它混合信号功能所用的电源。然而,PLL的关键元件——“压控振荡器”(VCO)的实用技术要求并未随之大幅降低。许多高性能VCO设计仍然采用分立电路来实施,可能要求高达30 V的电源电压。这就给当今的PLL或RF系统设计师提出了挑战:低压PLL IC如何与高压VCO实现接口。电平转换接口通常利用有源滤波电路来实施,这将在下文讨论。本文将分析说明PLL的基本原理,考察采用高压VCO的PLL设计的当前技术水平,讨论典型架构的利弊,并介绍高压VCO的一些替代方案。

PLL基本原理

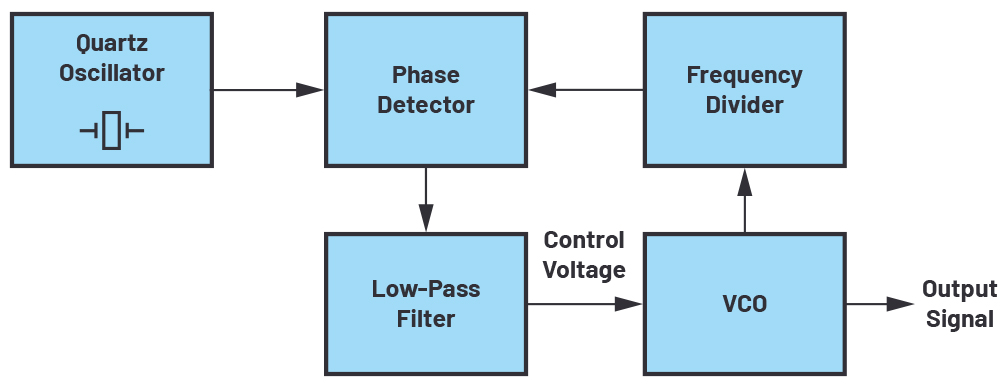

锁相环(图1)是一个反馈系统,其中相位比较器或鉴相器驱动反馈环路中的VCO,使振荡器频率(或相位)精确跟踪所施加的参考频率。通常需要用滤波电路,对正/负误差信号求积分并使之平坦,以及提高环路稳定性。反馈路径中常包含分频器,使输出频率(VCO的范围内)为参考频率的倍数。分频器的频率倍数N可以是整数,也可以是小数,PLL相应地称为“整数N分频PLL”或“小数N分频PLL”。

图1. 基本锁相环

PLL是负反馈控制环路,因此达到均衡时,频率误差信号必须为零,以便在VCO输出端产生精确且稳定的频率N × FREF。

PLL有多种实施方法,根据所需频率范围、噪声和杂散性能以及物理尺寸,可以采用全数字式、全模拟式或混合电路。目前,高频(或RF)PLL的常用架构既含有全数字式模块,如反馈分频器和鉴相器等,也含有高精度模拟电路,如电荷泵和VCO等。混合信号PLL的主要特点包括:

- 参考频率:稳定、精确的基准频率,RF输出将锁相于该频率;通常源于晶振或温度控制晶体振荡器(TCXO)。

- 鉴频鉴相器(PFD):从参考信号和反馈信号中产生相位误差信号。

- 电荷泵:将误差信号转换为与相位误差成比例的正/负电流脉冲串。

- 环路滤波器:对来自电荷泵的电流脉冲求积分,向VCO调谐端口提供干净的电压。

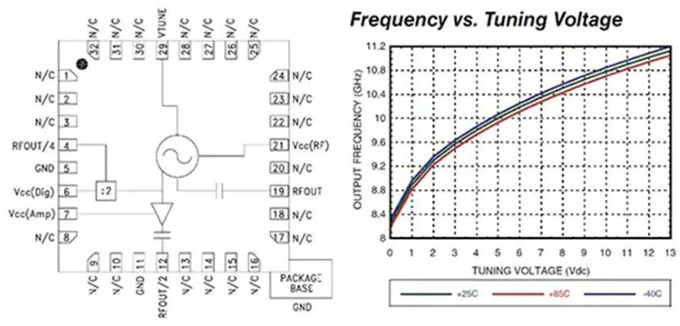

- VCO:根据调谐端口上的电压(Vtune),输出一个频率。VCO具有增益KV,用MHz/V表示。VCO输出频率与输入控制电压的基本关系表达式为fo = fc + Kv (Vtune),其中fc为VCO偏移频率。

- N分频器:将输出频率倍除为PFD或参考频率。可以简单地采用整数倍除,也可以采用小数倍除(小数N分频器),采用后者的越来越多。小数分频器的实施很简单,只需切换整数分频器的除数便可获得小数平均值(例如,要获得平均值4.25,可以计数到4三次并计数到5一次;这样就计数了17个脉冲,并生成了4个脉冲,因此频率比为17/4 = 4.25)。实践中,借助高分辨率噪声整形转换器所用的技术可以实现更好的效果。因此,小数方法通常采用Σ-Δ结构实施,它具有杂散频率少的优势。

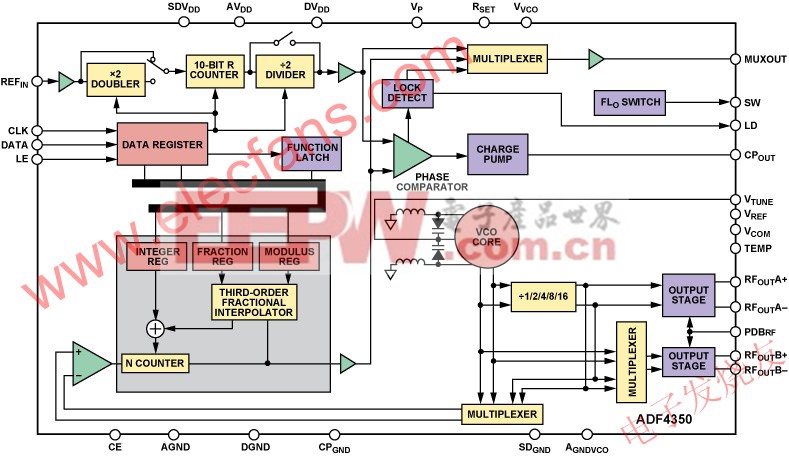

图2显示了当前器件的高度集成电路示例,这是集成VCO的小数N分频PLL IC ADF4350宽带频率合成器的框图,其输出频率范围为137.5 MHz至4400 MHz。(集成VCO的宽带宽PLL部分简要描述了其功能。)

图2. ADF4350 PLL频率合成器框图

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

分频器相关文章:分频器原理 电荷放大器相关文章:电荷放大器原理 lc振荡电路相关文章:lc振荡电路原理 鉴相器相关文章:鉴相器原理 晶振相关文章:晶振原理 绝对值编码器相关文章:绝对值编码器原理 数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理 锁相放大器相关文章:锁相放大器原理

评论