全同步数字频率计的 VHDL设计与仿真

1 引 言

频率测量不仅在工程应用中有非常重要的意义,而且在高精度定时系统中也处于核心地位,±1个计数误差通常是限制频率测量精度进 一步提高的重要原因。由于测频技术的重要性,使测频方法也有了很大的发展,常用数字频率测量方法有M法,T法,和M/T(等精度测量法)法。M法,T法, 和M/T法都存在±1个计数误差问题:M法存在被测闸门内±1个被测信号的脉冲个数误差,T法或M/T法也存在±1个字的计时误差,这个问题成为限制测量 精度提高的一个重要的原因。全同步频率测量法[1],从根本上消除了限制测量精度提高的±1个计数误差问题,从而使频率测量的精度和性能大为改善。

基于对FPGA器件和EDA技术以及全同步测频方法的研究[2,3],介绍一种利用FPGA实现DC~100 MHz全同步数字频率计的实现方法,并给出VHDL实现代码和仿真波形。整个系统在研制的FPGA/CPID实验开发系统上调试通过。本设计采用了高集成度的现场可编程门阵列(Field Program-mable Gata Array,FPGA)Flex EPF10k20TCl44-4芯片[4],通过软件编程对目标器件的结构和工作方式进行重构,能随时对设计进行调整,使得本设计具有集成度高、结构灵活、开发周期短、可靠性高的优点。

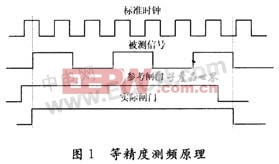

在文献[2,5]中所描述的等精度频率测量方法中,其测频原理如图1所示。

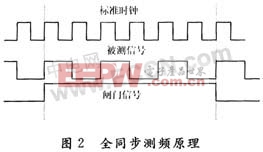

其 误差与闸门时间和标准时钟频率有关,闸门时间越长,标准时钟频率越高,误差越小。因此,用等精度测频法时所取的标准时钟频率比较高(10 MHz以上),因此±1计数误差相对很小。标准时钟频率不可能无限制提高,并且随着频率提高,产品成本成倍增加,对于生产应用没有意义。因此本设计用改进 的等精度频率测量方法--全同步测量来实现数字频率计的设计。在全同步的情况下,闸门信号不仅与被测信号同步,还与标准时钟同步。其原理图如图2所示。

2 全同步测频原理简述

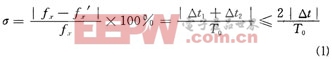

由文献[1,6]可知:设开启闸门时脉冲同步时间差为△t1,关闭闸门时脉冲同步时间差为△t2,脉冲同步检测最大误差为△t,则有:△t1≤△t,△t2≤△t。频率测量的相

对误差如式(2)所示:

由式(1)可知,误差只与脉冲检测电路准确度有关,显然,控制△t来提高频率测量精度是有效的,而且实现走来比提高标准时钟频率更容易。

在以上分析的基础上,本设计采用FPGA来实现全同步数字频率计。其系统原理框图如图3所示。由图3可知,设计的绝大部分由FPGA完成,只有脉冲同步检测电路由74LS系列与非门来实现,以及显示部分由数码管构成。

3 全同步数字频率计模块设计

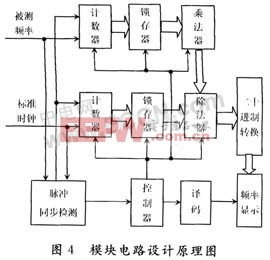

由系统原理框图3,则其FPGA内部模块电路设计原理如图4所示。

设 计原理图主要由以下几部分组成:脉冲同步检测电路、2个计数器、2个锁存器、控制器、乘法器、除法器、泽码电路等组成。工作原理如下:被测频率与标准时钟 分别送给脉冲同步检测电路与2个计数器,当脉冲同步检测电路检测到被测频率与标准时钟相位同步时,脉冲同步检测电路发出同步信号,2个计数器开始计数,当 脉冲同步检测电路再次检测到间步信号时,义发出同步信号,计数器停止计数。同时计数器的计数值锁存到锁存器,时序乘法器从锁存器中取得被测频率的计数值与 标准时钟频率进行乘法运算,然后再将乘法器运算所得的值与标准时钟的计数值送给除法器,乘法器的结果为被除数,标准时钟的计数值为除数,运算所得结果就是 被测信号的频率,然后冉经过二卜进制转换变成BCD码,送给数码管显示。本设计采用10 MHz的标准时钟,由于乘法器输入是27位二进制,相当于9位10进制数,而10 MHz的标准时钟为107Hz,因此用被测频率的计数值乘以108可得到一位小数点。

3.1 脉冲同步检测电路

脉冲同步检测电路 没计原理图如图5所示。U1~U8为74LS系列与非门,同步检测电路利用门电路的延时来构成。当被测信号及标准时钟都处在低电平时,U1,U2输出为高 电平,U3,U4的输出为高电平,U5,U6输出为低电平,则U8输出为低电平。当被测信号(Fx)及标准时钟的上升沿同时到来时,由于门电路具有延时特 性,因此U1,U2并不马上变为低电平,而是要经过一个延时才变为低电平。于是U3,U4的输入端都是高电平,则U3,U4

输出为低电平,U5,U6的输出为高电平,则U8输出为高电平。但是当且仪当Fx与CLK的上升沿在在延时时间内同时到达时U8才会输出高电平。74LS系列与非门的延时最小为4 ns,最大为15 ns,因此最大误差为11ns。根据公式(2)得:![]()

当T0为1 s时,其精度可达到10-7,如再减小相位误差,则可提高频率计的精确度。

评论