基于快速傅里叶IP核的数字脉压处理器的实现

2.2.2 脉冲压缩模块的时序设计

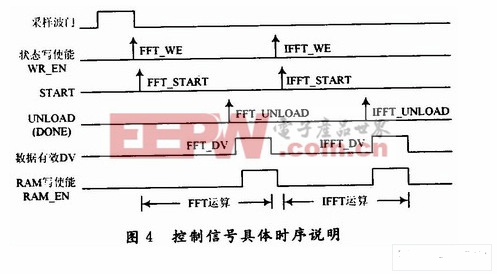

由于FFT和IFFT的逻辑运算功能已经在IP核中实现,因此时序设计便显得尤为重要。在FFT(或IFFT)运算单元中,主要的状态与时序控制信号及其功能描述如表1所示。

在采样距离门有效期间,将样本数据写入FIFO中进行缓存。采样结束后,通过FFT单元的写使能信号(NFFT_WE和FWD_INV_WE)将NFFT=010 10及FWD_INV_WE=1写入状态控制寄存器设定工作模式,接着启动START信号进行FFT运算,写使能信号与sTART之间仅差1个时钟周期。运算结束后,DONE信号有效1个时钟周期,输出使能信号UNLOAD与DONE同步,经过7个时钟周期后数据有效信号DV开始有效,FFT运算结果开始流水输出,同时与匹配滤波器的系数相乘,并存入RAM中。由于乘法运算的固有延迟,写使能RAM_EN延迟DV信号2个时钟周期。存储结束时,IFFT单元的写使能信号同时有效,并设定NFFT=01010及FWD_INV_WE=0,接着启动START信号进行IFFT运算。运算结束后,DONE信号(与UNLOAD同步)再次有效,IFFT运算输出结果在DV信号有效期间直接写入RAM中。单个PRT内各控制信号的具体时序说明如图4所示。

2.2.3 块浮点数据格式

在数字信号处理系统中,数据表示格式可分为定点制、浮点制和块浮点制,它们在实现时对系统资源的要求不同,工作速度也不同,有着不同的适用范围。定点表示法使用最多,简单且速度快,但动态范围有限,需要用合适的溢出控制规则(如定比例法)适当压缩输入信号的动态范围,但这样会降低输出信号的信噪比。浮点表示法的优点是动态范围大,可避免溢出,能在很大的动态范围内达到很高的信噪比,主要缺点是系统实现复杂,硬件需求量大,成本和功耗高,而且速度较慢。

块浮点表示法兼有定点法和浮点法的某些优点,是以上2种表示法的结合。这种表示法首先对一组数据进行检测,归一化最大数的小数部分,再建立适当的指数。接着把剩下数据的小数部分转化为合适的数,使它们可以使用最大数的指数。块浮点算法的主要优点是:大动态范围、低截断(或舍入)噪声,是一种有效的数据表示形式。从芯片实现角度上看,块浮点表示法能够保证较高的信号处理质量,尤其适用于FFT运算的场合。脉压模块中的FFT核带有块浮点运算的功能,整个运算过程中的数据格式表示如图5所示。

ADC输入数据为14 b的二进制补码形式,对其低位补零扩展为16 b(IP核要求的输入精度)后送入FFT运算单元,输出结果为16 b的定点数以及指数EXP1。复乘包括乘法和累加运算,即FFT结果与匹配系数进行16 b×16 b的乘法运算,所得结果再进行加法运算;在进行加法运算前,所有数据扩展为33 b以防止溢出的发生,最终数据截取高16 b送入IFFT处理单元,输出为16 b的定点数和指数EXP2,将其与EXPl相加后得到指数EXP。脉压的最终结果即为IFFT后的16 b定点数以及指数EXP,两者分别存储在FPGA片内RAM中。

2.3 脉冲压缩模块的测试

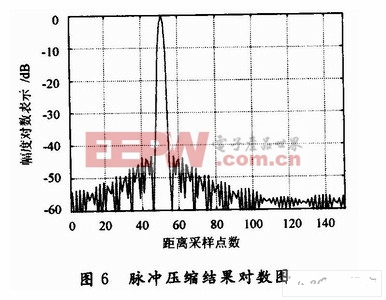

设输入理想LFM信号参数如下:带宽B=40 MHz;时宽T=6μs;系统样本速率为60 MHz;使用海明窗加权。在上述条件下,脉冲压缩系统的输出结果对数图如图6所示。

在图6中,横轴代表距离采样单元,即系统最小距离分辨率。通过系统实际处理结果与Madab仿真结果的对比验证了设计的正确性和实用性。

3 结语

系统采用ADS5500完成14位、60 MSPS的数据采集,并在FPGA中实现1 024点的数字脉冲压缩。设计采用并行流水方式提高工作速度,而块浮点算法则充分保证运算的精度。IP核的复用大大降低硬件规模,从而使整个系统具有高速度、高精度和低功耗的特点。本文引用地址:http://www.eepw.com.cn/article/185667.htm

评论