一种高性能CMOS电荷泵的设计

摘要: 设计了一种用于电荷泵锁相环的CMOS电荷泵电路。电路中采用3对自偏置高摆幅共源共栅电流镜进行泵电流镜像,增大了低电压下电荷泵的输出电阻,实现了上下两个电荷泵的匹配。为消除单端电荷泵存在的电荷共享问题,引入了带宽幅电压跟随的半差分电流开关结构,使电荷泵性能得以提高。设计采用0.18μm标准CMOS工艺。电路仿真结果显示,在0.35~1.3 V范围内泵电流匹配精度达0.9%,电路工作频率达250 MHz。

关键词: 电荷泵;锁相环;自偏置共源共栅电流镜;电压跟随

CMOS电荷泵锁相环(Charge Pump Phase-Locked Loop,CPPLL)具有高速、低功耗、低抖动、低成本等优点,在频率合成、时钟恢复等电路中被广泛采用。作为电荷泵锁相环里的一个关键模块,电荷泵在电路实现时,往往存在着开关延迟、充放电电流失配、电荷注入及电荷共享等非理想效应。对于高性能锁相环的设计而言,应尽量减小相位噪声及杂散的产生,使输出电流更平滑,输出电压谐波分量更低,减小开关延迟现象。文中提出了一种基于伪差分结构的具有高输出阻抗和高充放电流匹配率的电荷泵电路。

1 电荷泵设计分析

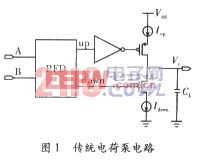

电荷泵主要功能是将鉴频鉴相器(PFD)的输出信号up和down转换为模拟的连续变化的电压信号,用于控制压控振荡器(VCO)的振荡频率。当PFD的up输出信号起作用时,电荷泵的电流源对环路滤波器进行充电,VCO的压控端电压升高,VCO的振荡频率也相应改变。反之,down信号使电荷泵电流沉对环路滤波器进行放电,VCO的压控电压信号降低。当VCO振荡频率和相位与参考信号相同时,电荷泵的输出信号应该保持一个常值。但是传统的电荷泵,如图l所示,存在多种非理想效应,比如电荷泄漏、充放电电流失配、电荷共享、泵开关的延迟等。一个好的电荷泵设计应该力求把以上情况降到设计规范之内。

1.1 电流失配

当up和down信号控制电荷泵充放电时,会产生电流失配和泵开关时间延时问题。由此引起的系统相位偏差表达式如(1)所示

其中,△ton,Tref,I和△I分别表示PFD开通时间、参考时钟周期、CP电流和充放电流偏差。从式(1)可知,Tref不变的情况下,减小△I,△ton和增大I有利于减小系统相位偏差。但是为了克服PFD的死区效应,一般需要保持一定的开通时间,所以,减少失配电流和增大电荷泵电流是减小PLL相位误差的行之有效的手段。

评论