一种12位50 MS/s CMOS流水线A/D转换器

摘要:采用TSMC 0.18 μm 1P6M工艺设计了一个12位50 MS/s流水线A/D转换器(ADC)。为了减小失真和降低功耗,该ADC利用余量增益放大电路(MDAC)内建的采样保持功能,去掉了传统的前端采样保持电路,采用时间常数匹配技术,保证输入高频信号时,ADC依然能有较好的线性度;利用数字校正电路降低了ADC对比较器失调的敏感性。使用Cadence Spectre时电路进行仿真。结果表明,输入耐奎斯特频率的信号时,电路SNDR达到72.19 dB,SFDR达到88.23 dB。当输入频率为50 MHz的信号时,SFDR依然有80.51 dB。使用1.8 V电源电压供电,在50 MHz采样率下,ADC功耗为128 mW。

关键词:A/D转换器;流水线结构;时间常数匹配;数字校正

0 引言

A/D转换器(ADC)作为数字世界与真实世界的接口已经成为了现代电子系统不可或缺的一部分。在各种类型的ADC中,流水线结构是当今满足高速高精度要求的重要实现手段。在一些需要10位以上转换精度,数十兆转换速率的场合,如无线通信、雷达、数字视频广播处理等领域,流水线ADC得到了极广泛的应用。传统的流水线ADC前端总是配置有采样保持电路(SHA)。SHA除了自身消耗一定的面积和功耗外,还引入了很大的噪声,是流水线ADC的主要噪声源之一。由于高的噪声需要用大电容来克服,因此,取消SHA会允许系统使用更小的电容,这对减小系统功耗有决定意义。另外,采样保持电路还会因为让输入信号混入谐波成分而给ADC带来失真。在ADC前端使用SHA的唯一原因是由此可以避免当输入信号频率较高时,ADC的性能受到孔径误差的限制。

本文设计了一个没有SHA电路的12位50 MS/s的流水线ADC。通过使用时间常数匹配技术来抑制高频输入时产生的孔径误差。利用数字校正电路降低、ADC对比较器失调的敏感性。结果表明,输入耐奎斯特频率的信号时,电路SNDR达到72.19 dB,SFDR达到88.23 dB。当输入频率为50 MHz的信号时,SFDR依然有80.51 dB。

1 系统结构设计

流水线ADC由多级级联而成,对于级数和每级的精度都有不同选择。使用每级1.5位的结构可以多产生1位冗余位来进行数字冗余修正,大大减小比较器失调造成的影响;其次,这种结构的反馈系数是0.5,运放可以获得较大的闭环带宽。

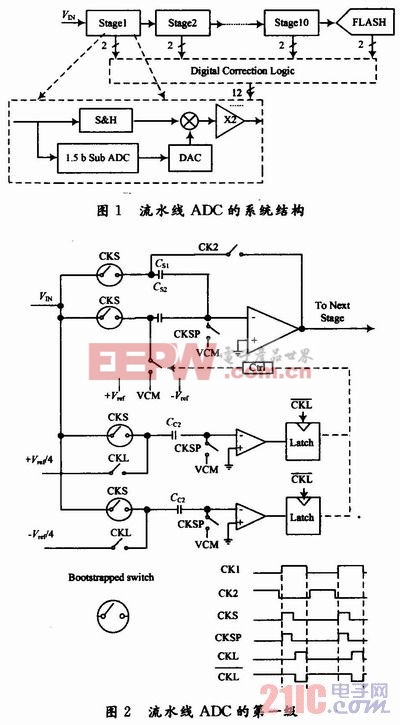

图1是ADC结构示意图。整个流水线由10级,每级1.5位的子级电路和1个2位的快闪型ADC(FLASH ADC)组成。输入信号直接输入到第一级,经过逐级转换,把得到的22位数字输出送入数字误差校正单元进行校正。最后输出12位的数字码。

由于没有SHA模块,故利用第一级电路中经修改过的余量增益电路(MDAC)替代SHA完成对输入信号的采样保持。具体的实现方式如图2所示。

图2中MDAC由运算放大器,采样电容Cs1,Cs2,编码控制电路及一系列开关构成。Cc1,Cc2和2个比较器构成子A/D转换器(Sub ADC)。第1级电路的时钟被分为了三相。输入信号在CKSP结束时被采样到Cs1,Cs2,Cc1,Cc2上。为了保持高线性度,输入开关采用了栅压自举(Boot-strapped)开关。在CKL相时,Cc1,Cc2与输入参考电压相连。Cc1,Cc2与比较器相连接的极板一侧会感生出输入参考电压与输入信号的差值。把这个差值送入比较器即可得到输入信号与参考电平的大小关系。当CKL结束时,锁存器锁存比较结果。而编码电路则根据比较结果生成控制码供MDAC求值时使用。在CK1相位时,Cs1与输出相连,Cs2根据控制码与不同的参考电平相连,MDAC开始求值。

第2~10级电路使用传统的每级1.5位的结构。同时,由于每级电路对精度的要求逐渐放低,因此可以在每级使用不同规格的运放以降低功耗与面积。本文使用了3种功耗依次递减的运放。可以设计更多的运放,以进一步降低功耗。

评论