三模冗余在ASIC设计中的实现方法

摘要:星载计算机系统处于空间辐照环境中,可能会受到单粒子翻转的影响而出错,三模冗余就是一种对单粒子翻转有效的容错技术。通过对三模冗余加固电路特点的分析,提出了在ASIC设计中实现三模冗余的2种方法。其一是通过Syno-psys的综合工具DesignCompiler对原设计进行综合,然后修改综合后的门级网表再次综合;其二是直接建立采用三模冗余加固的库单元。

关键词:三模冗余;DesignCompiler综合;库单元;专用集成电路

0 引言

航天器在空间中飞行时,一直处在带电粒子构成的辐射环境中。在这种辐射环境中微处理器可能会因为单粒子扰动而中断正常功能从而导致灾难性事故。这主要涉及到2方面的问题,辐射总剂量效应和单粒子效应的问题,单粒子效应又分为单粒子翻转(SEU)和单粒子闭锁(SEL)2个方面。单粒子翻转效应能够导致数字电路的存储单元中的某一位因受到干扰而发生翻转,从而引起存储内容的变化,还可在组合逻辑电路的输出上引入一个短暂的脉冲,单粒子翻转效应是目前导致处理器运行失效的主要原因。星载计算机系统中处理器性能的稳定与可靠在整个系统的稳定与可靠性中占有重要地位,因此必须对电路进行加固,三模冗余技术是一种对单粒子翻转有效的容错技术,能够极大地提高电路的可靠性。

1 三模冗余介绍

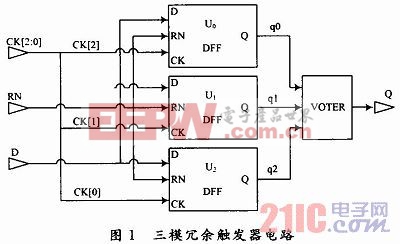

三模冗余(TMR)技术是一种时序电路加固技术,其基本思想是对于待加固模块生成2个相同的模块,再通过多数表决输出,这样即使有一个模块发生故障电路依然可以正常工作。三模冗余在结构上又有空间冗余和时间冗余之分,时间冗余就是3路时钟信号之间存在一定延迟,延迟值应大于SEU翻转的最大脉宽。时间冗余的作用是对于时序电路的输入毛刺,最多只有一路时钟会采样到错误值,因此可以有效地防止组合逻辑毛刺所带来的错误。图1是采用普通时空三模冗余加固的触发器的电路图(以后简称TMR触发器),其中VOTER为多数表决器的组合电路。

虽然三模冗余技术可以极大地提高系统的可靠性,但是代价也是巨大的。由TMR的基本结构不难看出采用TMR技术的2个缺点:首先由于进行了硬件冗余导致芯片面积增大到原来的3倍多;其次由于三路时钟信号之间的延迟和在输出端加入了表决电路,在关键路径上引入了额外的延时,导致电路的运行速度下降。

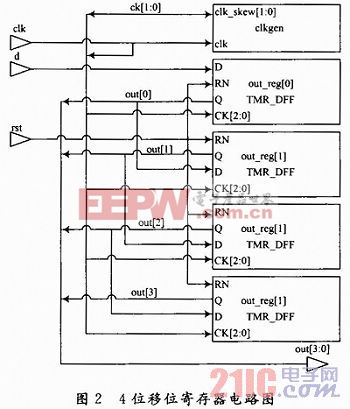

如果设计中2个触发器之间的关键路径延迟太短(比如移位寄存器),图1的三模冗余电路结构在运行中可能会出现电路输出不定态和电路状态错误的问题,图2是一个采用三模冗余加固的4位移位寄存器的电路图,图中的TMR_DFF模块的电路如图1所示。

评论