PCB板时钟电路的电磁兼容设计

摘要:为了研究PCB集成电路板中时钟引起的电磁兼容问题,采用了仿真数值计算的方法,对时钟电路的电磁兼容设计时几种主要影响因素进行分析研究,确定了在PCB集成电路板设计时的时钟选择原则,以及时钟电路电磁兼容设计时的具体对象和内容,通过优化时钟设计的布局和布线来达到提高了PCB板电磁兼容设计。最后提出了可以有效切断PCB板上时钟干扰传播途径的几种措施,为工程技术人员提供一种解决相关问题的思路。

关键词:PCB板;时钟信号;电磁兼容设计;仿真数值计算

0 引言

众所周知,电磁兼容的3要素是电磁干扰源、被干扰对象和传播电磁干扰的途径。PCB板上安装的时钟信号是一种引起PCB板电磁兼容问题的常见而又非常重要的辐射源。尽管时钟信号与其他数据信号、控制信号的逻辑电平一般都是一样的,翻转速率一般也没有太大的差别(大多数总线数据率与时钟信号翻转速率之比是1:1或者1:2),但由于时钟信号之所以更容易接近或者超过辐射发射的限值,主要原因是时钟信号是比较严格的周期信号,其在频域的能量主要集中在某些频点上,而数据信号是非周期信号,在频域上的能量也是比较分散的。因此,良好的时钟电路设计是PCB板的电磁兼容设计的关键。

1 时钟信号的频谱

根据傅里叶展开可以得到,一个幅度为A,周期为T,脉冲宽度为t0,上升下降时间为tr的梯形时钟波形,其在n次谐波处的谐波分量为:

![]()

式中C(n)为n次谐波处的谐波分量,单位:V或dBμV。

从上面梯形时钟波形的傅里叶级数可以看出,影响时钟信号辐射强度的因素有时钟波形的幅度A、占空比(t0+tr)/T、时钟周期T(或者时钟频率f)、以及时钟波形的上升时间和下降时间。其中时钟信号的幅度与其产生的干扰直接线性相关,上升时间和下降时间对时钟高次谐波的影响至关重要。

2 时钟频谱的影响因素

2.1 时钟上升时间对辐射的影响

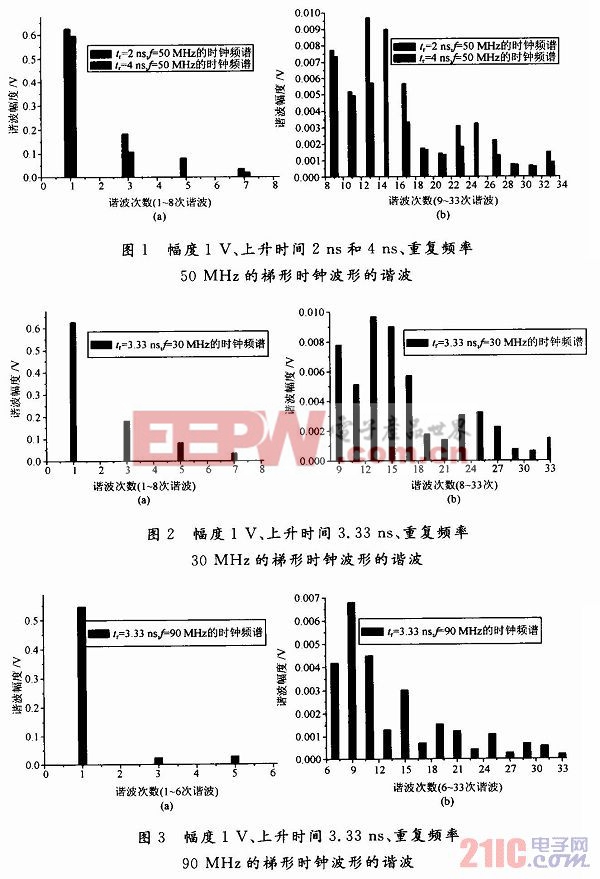

假设有2个时钟信号,幅度都为1 V,频率都为50 MHz,上升时间分别为2 ns和4 ns。根据上面的傅里叶变换可以得到2个时钟信号的频谱分布,如图1所示。

DIY机械键盘相关社区:机械键盘DIY

评论