创新的低待机损耗解决方案应用于反激式转换器

节能技术在当今电子行业中,已成为一个热点,其中最受关注的是待机功耗。相当一部分产品有一定比例的时间处于轻载或待机(空载)工作模式,而“能源之星”等规范标准在致力于提升电子设备所用电源适配器工作效能的同时,也注重提升轻载效能及降低待机功耗。为了降低待机功耗,来满足最新的“能源之星”规 范,飞兆半导体已将许多全新省电技术与功能应用于反激式转换器 (flyback converter)。根据实验的结果,在交流输入电源为230V情况下,将可以实现30mW极低的待机功耗。

本文引用地址:https://www.eepw.com.cn/article/176243.htm本篇文章将探讨一些创新技术,包括:内建高压启动电路、待机时的极端脉冲降频模式(Deep Burst Mode)、极低的工作电流以及高压组件放电 X电容技术 (Ax-CAP™),以便节省放电电阻的功耗与使用,以上这些省电方法将使电源设计转向低成本、省电和高效率的最佳电源解决方案。

简介

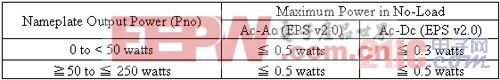

美国能源之星(ENERGY STAR) 从2009 年1 月起,针对无载的电源消耗订定了严格的规范,表一所列是在不同的额定瓦数下的详细规定。

表一、 EPS v2.0 无载时能源损耗标准

当前,能源之星规范已不足以作为新一代电子产品对节能的要求,世界大厂如苹果、惠普和戴尔等响应环保议题,已经积极提出更为严苛的规范,对此,飞兆半导体已将无载损耗门槛降低至30mW。

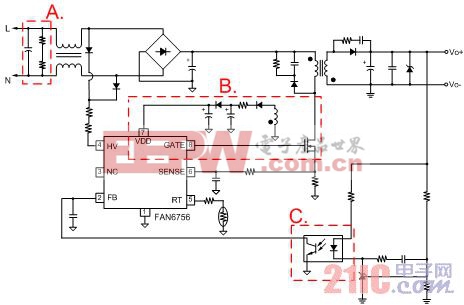

图一中为典型的反激式转换器,下面分析电源转换器在无载下的损耗。主要的损耗 (不含变压器损耗) 包括了开关损耗(Switching loss) 以及由控制电路组件所造成的损耗。表二分别对这些主要损耗列出损耗估算式和一般的改进对策。

图一、典型的反激式转换器电路

表二、无载的主要损耗分析表(不含变压器损耗)

这些主要的无载或极轻载损耗,如图一所示将被划分A、B和C三个区域来讨论,应用飞兆半导体的创新技术,可分别降低这三部分的损耗。

首先为A区域,A区域里有消除电磁干扰的X电容器与并联的安规放电电阻,基本上这器件的选用必须符合安规等式(1),其中安规规定的放电时间须满足于1秒 内;并联接线方式势必于安规电阻上会有电能的功耗,且与输入电源电压的平方成正比增加,这个功耗可利用等式(2)得知,例如当输入电源为264V且放电电 阻为2MΩ时,将会有可观的35mW在此区域消耗。

FAN6756使用创新的内部高压器件对 X电容放电技术(Ax-CAP™),消去放电电阻的功耗并不需此电阻的使用仍可通过安规认证。

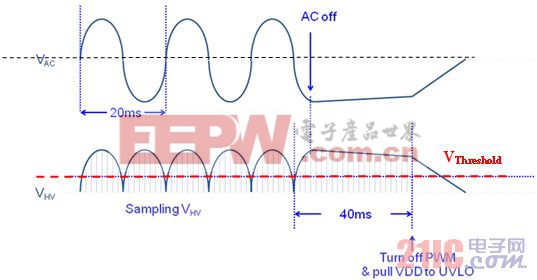

在图二中,当于无载或极轻载时拔去输入电源插头时,交流电压(VAC)会保持在一个近似稳定的电压加在X电容器两端,FAN6756通过HV引脚的取样逻辑去得知VAC 的电压变化,这个逻辑电路内部设置有一个比较电压 (VThreshold)去检测是否VAC电压值在芯片设定的延时时间(debouncing)内始终高于这个比较电压 (VThreshold),如果确认此时为拔插头的状况,FAN6756 将HV脚通过内部开关管连接至VDD,利用高压启动电流将X电容上的电荷释放;此功能只在无载或极轻载条件下有效,而取样逻辑的判断时间约为40ms。

图二 、拔去输入插头的相关电压行为

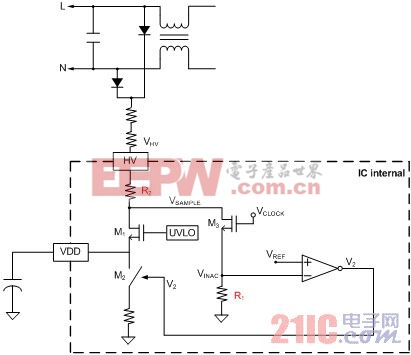

从图三中可得知HV引脚功能包括高压启动、输入电压取样电路和X电容放电机制, M1开关是连接高压和VDD之间的桥梁,由UVLO来控制。M1开关和R2路径用来实现高压启动功能, M3开关是通过一个频率信号控制来做输入电压取样控制,R2和R1分压形成一个输入电压 (VINAC)的取样到比较器的反相输入端;VINAC是用来侦测输入电源的电压值;VREF是用来做为放电判断的参考电压。假如VINAC总是高于 VREF,M2开关将被闭合,VDD电位将被放电到VDD_OFF,使得UVLO保护触发,UVLO保护将打开 M1开关并关闭M2,HV引脚将从X电容汲取所需的启动电流对VDD的电容重新充电,以达到放电功能。

图三、HV引脚的逻辑电路图

接下来介绍如何改进B区域的损耗,于B区域致力的目标是降低功率晶体管和 IC的功耗。功率晶体管主要功耗因素有VDD电压、Burst的时间长短和开关频率(FSW) 如等式(3)所示,在一般工作模式中(非保护模式),FAN6756使用创新技术去产生极低的UVLO电压约为6.5V,所以辅助绕组电压设定将可大幅降低;其次将Burst时间延长,降低在无载或极轻载时的工作频率与脉冲频率(fBurst)使FAN6756进入极端脉冲降频模式,进而降低开关损耗;另一方面在栅极无输出的情况下让IC的工作电流(IOP_Gate-off) 降低,以减少如等式(4)所示的IC静态损耗。图四为于高压无载条件下的实际量测波形,辅助绕组电压平均值大约为12V而栅极与栅极驱动 之间的距离大约为1.12秒,此种方法可以降低 B 区域**率晶体管和 PWM IC 的功耗。图五定义出等式 (3) 与等式 (4) 中的相关参数。

电容器相关文章:电容器原理

电荷放大器相关文章:电荷放大器原理

评论