利用高速ADC设计用于汽车的LIDAR系统

随着模拟技术的不断改善,LIDAR在很多具有广泛前景的领域得到应用,ADC技术的发展可以实现更高精度和更低功率的系统设计。

汽车系统设计师开发成熟的LIDAR系统,可以根据交通情况自动地控制汽车速度和刹车系统,这样的系统还能动态地控制与其它汽车和障碍物的距离,甚至能管理像气囊这样的安全功能。该技术的发展大大提高了驾驶员的舒适性和安全性。

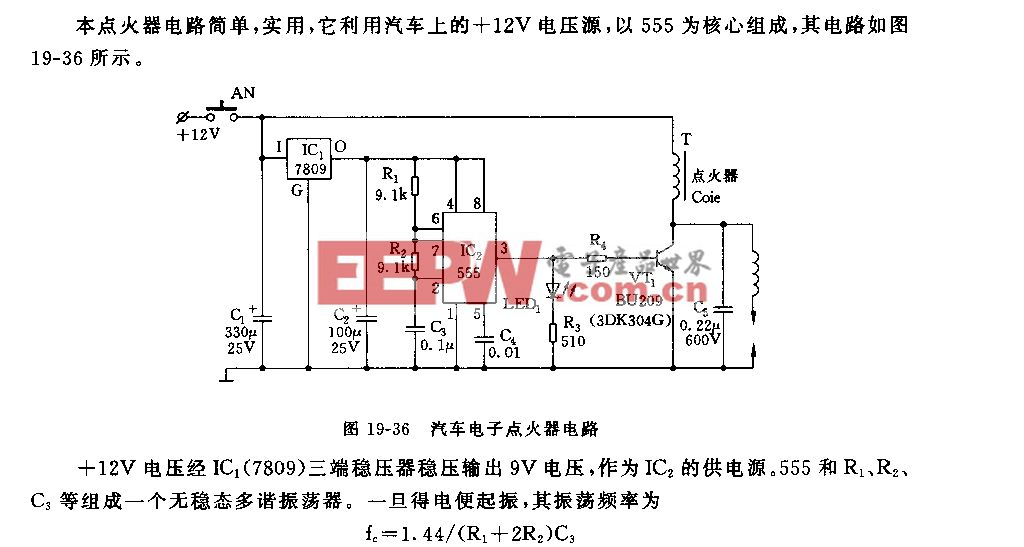

图1LIDAR组成框图

无论是什么应用,这种系统的接收路径上的关键模拟器件都是ADC,它用于将从近处或远处目标发射回来的窄脉冲信号进行数字化处理。这种ADC需要非常快的采样速率、很高的模拟输入带宽以及低功耗。图1显示了LIDAR系统的一个简化功能框图。

可选的系统实现方法

当前最常用的方法是具有相位比较功能的连续波(CW)激光和脉冲激光。CW激光系统的工作原理是:目标物体反射回一个原始发射信号的移相信号,接收器将收到的移相信号与原始信号进行比较,相位比较器的输出可以用于计算距离。正如其名所指,脉冲激光系统发射和接收短光脉冲信号。半导体脉冲激光用于要求低成本、低功耗、小尺寸和轻重量的应用中。半导体脉冲激光需要在接收器中采用非常快的ADC,这是当前最常用的方法,也是本文讨论的重点。

LIDAR系统可以测量的距离取决于以下几个因素:激光峰值功率、激光的发散性、光学系统和大气能见度、目标物体的反射特性以及检光器的灵敏度。能见度和反射系数决定于具体的应用,设计的灵活性很大程度上取决于激光源的功率和接收器的灵敏度。TOF测量的准确性取决于激光的脉宽以及所使用的ADC的速度和精度。

根据不同的应用需求,所用的激光功率在几毫瓦到几百瓦之间。半导体脉冲激光的距离计算公式基于功率以及其它的系统和大气条件,LIDAR系统相对于一个外部物体的往返距离计算公式是:距离=√ [(P * A* Ta * To)/(Ds * PI * B)]式中,P为激光功率,A为Rx光学系统面积(镜头或镜面),Ta为大气能见度,To为光学系统的能见度,Ds为检光器灵敏度,B为光束的辐射发散性。

对于接收器中的低功率激光检测,设计师具有三个基本的检光器选择:硅PIN检光器、雪崩光电二极管(APD)和光电倍增管(PMT)。APD广泛用于测量仪表和航空航天应用中,提供了其它检光器所不可比拟的高速和高灵敏度性能。

接收器中的APD将接收到的光脉冲信号转变为电信号,输出与入射光成正比的电流,用互阻抗放大器将这个输出电流转换为电压信号。好的互阻抗放大器应该具有高增益、高输入阻抗、超低电压和电流噪声以及低输入电容,它通常具有一个FET或MOS输入级用于满足这些要求。采用高性能器件可以达到输入噪声电压小于1.0 nv√Hz、电流噪声小于15 fA√Hz的性能。互阻抗放大器的输出通常在由ADC进行数字化之前转换为一种差分信号并进行放大。

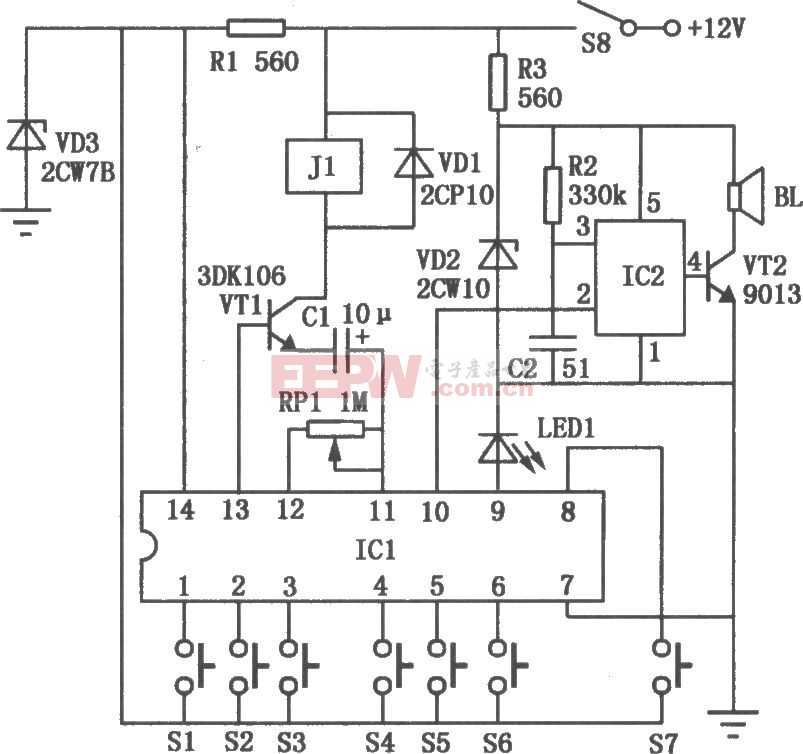

发送的脉冲信号通常被大气环境等因素衰减,导致发射脉冲信号与接收信号之间存在很大强度差异。发射器邻近的物体也可能会反射回高功率信号到接收器,这导致对接收系统苛刻的动态范围要求,这种接收系统必须具有足够的灵敏度来处理满功率脉冲或超低功率的脉冲信号。因此,100dB的动态范围要求并不鲜见,这种动态范围通常是在ADC之前的前端电路中采用可变增益放大器(VGA)或者数字VGA来实现的,如图2所示(CLC5526为数字VGA,ADC08D1000为双路低功耗、1.6GSPS的8位ADC)。

图2 在前端电路中采用数字VGA实现高动态范围

高采样速率提高LIDAR系统精度

距离测量可以达到的精度与ADC采样频率直接相关。由于光速C = 3E+08 m/s,而采样速率为1GSPS的ADC的时钟周期为1ns。在1ns的采样时间内,光的传播距离为0.3m。因此,在1GSPS采样速率下,分辨率为30cm/m。这意味着在任何距离下,采样速率为1GSPS时可以达到+/- 15cm的精度。随着采样速率的降低,误差将增加。

如前面所述,通过反射光脉冲的波长改变可以确定目标的某些物理特性,这称为多普勒位移。为测量窄脉冲波长的改变,需要采样速率为1GSPS或更高的ADC。

接收脉冲的形状也包含目标物体的特性信息。只有非常高的过采样率才能确定脉冲形状,过采样对于数字概念来说,还对处理增益有好处,更高的处理增益可以得到更高的信噪比(SNR)。

多个ADC的同步实现

多个ADC交替工作来增加采样速率,这个采样速率是单个器件目前尚不能达到的。增加采样速率的好处是可以得到更精细的脉冲形状和更高的时序精度。本文谈到的一个ADC固有的挑战是ADC输出数据流的同步。系统开发者必须准确地知道ADC输出的哪个字(word)对应于系统前端采样的脉冲。 为简化这种时间交替处理,采用ADC08Dxxx系列芯片能够准确地复位其采样时钟输入与数据输出时钟(DCLK)输出之间的关系,这种关系是由用户提供的DCLK_RST脉冲决定的。这样可以允许一个系统中的多个ADC的DCLK(和数据)输出转换可以与它们用来采样的共享CLK输入发生在同一时间点上。

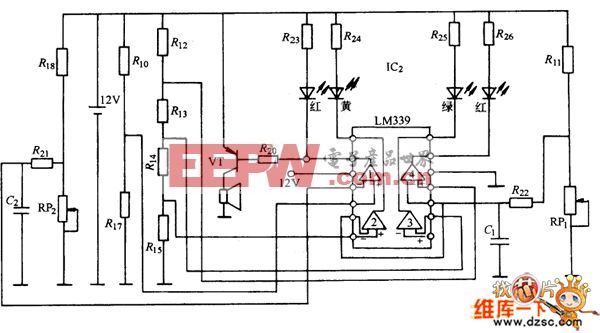

图3 DDR模式下DCLK的复位时序。

信号在FR04 PCB上的传输速度为20cm/ns(即每50ps1cm),如果ADC相互并不是很靠近的话,图3中的设计时间是难以实现的。

在这情况下,建议短时间(小于50ns)停止时钟,这样,在DCLK_Res置位期间维持交流耦合。推荐输入时钟采用交流耦合。交流耦合电容的时间常数是50 K?(内部偏置电阻)

评论