总线标准与层次结构

计算机部件要具有通用性,适应不同系统与不同用户的需求,设计必须模块化。计算机部件产品(模块)供应出现多元化。模块之间的联接关系要标准化,使模块具有通用性。模块设计必须基于一种大多数厂商认可的模块联接关系,即一种总线标准。

本文引用地址:https://www.eepw.com.cn/article/172822.htm总线的标准

总线是一类信号线的集合是模块间传输信息的公共通道,通过它,计算机各部件间可进行各种数据和命令的传送。

为使不同供应商的产品间能够互换,给用户更多的选择,总线的技术规范要标准化。

总线的标准制定要经周密考虑,要有严格的规定。

总线标准(技术规范)包括以下几部分:

机械结构规范:模块尺寸、总线插头、总线接插件以及按装尺寸均有统一规定。

功能规范:总线每条信号线(引脚的名称)、功能以及工作过程要有统一规定。

电气规范:总线每条信号线的有效电平、动态转换时间、负载能力等。

总线的发展情况

S-100总线:产生于1975年,第一个标准化总线,为微计算机技术发展起到了推动作用。

IBM-PC个人计算机采用总线结构(Industry Standard Architecture, ISA)并成为工业化的标准。先后出现8位ISA总线、16位ISA总线以及后来兼容厂商推出的EISA(Extended ISA)32位ISA总线。

为了适应微处理器性能的提高及I/O模块更高吞吐率的要求,出现了VL-Bus(VESA Local Bus)和PCI(Peripheral Component Interconnect,PCI)总线。

适合小型化要求的PCMCIA(Personal Computer Memory Card International Association)总线,用于笔记本计算机的功能扩展。

总线的指标

计算机主机性能迅速提高,各功能模块性能也要相应提高,这对总线性能提出更高的要求。总线主要技术指标有几方面:

总线宽度:一次操作可以传输的数据位数,如S100为8位,ISA为16位,EISA为32位,PCI-2可达64位。总线宽度不会超过微处理器外部数据总线的宽度。

总数工作频率:总线信号中有一个CLK时钟,CLK越高每秒钟传输的数据量越大。ISA、EISA为8MHz,PCI为33.3MHz, PCI-2可达达66.6MHz。

单个数据传输周期:不同的传输方式,每个数据传输所用CLK周期数不同。ISA要2个,PCI用1个CLK周期。这决定总线最高数据传输率。

总线的分类与层次

系统总线:是微处理器芯片对外引线信号的延伸或映射,是微处理器与片外存储器及I/0接口传输信息的通路。系统总线信号按功能可分为三类:

地址总线(Where):指出数据的来源与去向。地址总线的位数决定了存储空间的大小。

系统总线:

数据总线(What)提供模块间传输数据的路径,数据总线的位数决定微处理器结构的复杂度及总体性能。

控制总线(When):提供系统操作所必需的控制信号,对操作过程进行控制与定时。

扩充总线:亦称设备总线,用于系统I/O扩充。与系统总线工作频率不同,经接口电路对系统总统信号缓冲、变换、隔离,进行不同层次的操作(ISA、EISA、MCA)

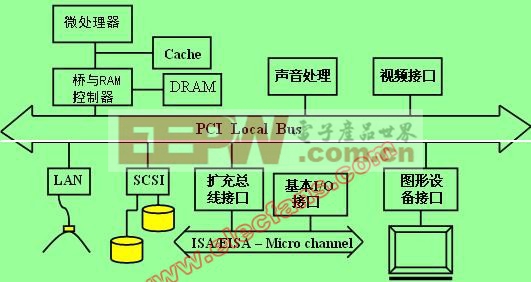

局部总线:扩充总线不能满足高性能设备(图形、视频、网络)接口的要求,在系统总线与扩充总线之间插入一层总线。由于它经桥接器与系统总线直接相连,因此称之为局部总线(PCI)。

总线层次结构

总线一个操作过程是完成两个模块之间传送信息,启动操作过程的是主模块,另外一个是从模块。某一时刻总线上只能有一个主模块占用总线。 总线的操作步骤: 同步总线定时:总线上的所有模块共用同一时钟脉冲进行操作过程的控制。各模块的所有动作的产生均在时钟周期的开始,多数动作在一个时钟周期中完成。 总线仲裁

总线操作

总线的操作步骤:

主模块申请总线控制权,总线控制器进行裁决。

主模块得到总线控制权后寻址从模块,从模块确认后进行数据传送。

数据传送的错误检查。

总线定时协议:定时协议可保证数据传输的双方操作同步,传输正确。定时协议有三种类型:

异步总线定时:操作的发生由源或目的模块的特定信号来确定。总线上一个事件发生取决前一事件的发生,双方相互提供联络信号。

总线定时协议

半同步总线定时:总线上各操作的时间间隔可以不同,但必须是时钟周期的整数倍,信号的出现,采样与结束仍以公共时钟为基准。ISA总线采用此定时方法。

数据传输类型:分单周方式和突发(burst)方式。

单周期方式:一个总线周期只传送一个数据。

数据传输类型:

突发方式:取得主线控制权后进行多个数据的传输。寻址时给出目的地首地址,访问第一个数据,数据2、3到数据n的地址在首地址基础上按一定规则自动寻址(如自动加1)。

基本概念

总线上可以连接多个主模块,它们均可占用总线传送数据。当出现多个主模块申请占用总线时,要进行仲裁,将总线控制权交给一个主模块。总线仲裁的主要方法有分布式仲裁与集中式仲裁两种方法。

菊花链式分布串行总线仲裁:每个主模块包含有总线控制逻辑,多个主模块分享总线。

所有主模块总线请求“线或”在一起,CPU响应信号级联传播,占用总线的模块发出忙信号。此方法优先级排定,灵活性差。

集中式并行总线仲裁

有一个集中的总线仲裁逻辑,各主模块的请求及响应信号独立。仲裁逻辑进行优先级判断,可有不同的仲裁策略。

评论