兼容51指令的8位MCU IPCORE设计

1 前言

本文引用地址:https://www.eepw.com.cn/article/170741.htm当前,在微电子及其应用领域正在发生一场前所未有的变革,这场变革是由片上系统(SOC)技术研究应用和发展引起的.从技术层面看SOC技术是超大规模集成电路发展的必然趋势和主流,它以超深亚微米VDSM(Very Deep Submicon)工艺和知识产权IP核复用技术为支撑。在众多的IP核中,MCU CORE以其在SOC中嵌入后能充分发挥其处理灵活、软件可升级、硬件开销少的特点,在很大程度上成为SOC芯片必需模块。INTEL公司的MCS-51系列MCU 可以说是目前国内应用时间最长、最普及、可获得应用资料最多的功能强大的8位MCU , 所以建立兼容51指令MCU可综合IP核对于各种嵌入式系统和片上系统(SOC)的应用具有重要意义。

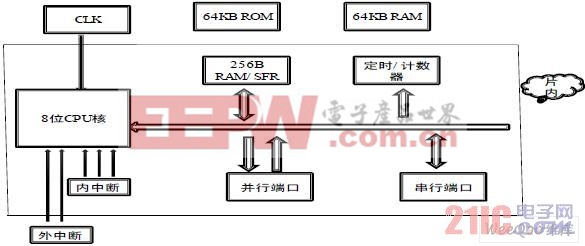

图1 IPCORE 内部结构

2 总体构架设计

本设计采用自顶向下的设计方法成功设计了与MCS-51 系列微处理器指令集完全兼容的8位嵌入式MCU核, 此核的内部结构如图1所示(整个设计过程也是围绕其产开)。

3 核内单元(主要单元设计的概述)

3.1 ALU 单元的设计:

ALU单元由一些基本操作功能模块(加/减法模块、乘法模块、除法模块、十进制调整模块和逻辑模块)构成,整个操作是通过多路选择器来完成的。在ALU单元的结构上,将乘、除法单元各自独立出来完成算术运算指令中的乘、除法运算。这样可以回避传统典型微处理器基于累加器ACC的ALU结构,并且由于ALU单元被设计成纯组合逻辑,因而速度较快,从而提高算术运算指令的执行效率。

3.2 时序设计

主要从简化控制器设计、提高核的性能出发,本设计没有采用Intel MCS-51双相时钟的复杂时序设计,而是采用单相时钟(单相时钟因为在时序和传输上比较简单可靠,被一些高性能芯片使用)、全同步设计,所有时序电路均采用边沿触发的触发器。采用单相时钟全同步设计会使芯片面积有所增加,但降低了设计的复杂度,减少了生产工艺不确定性对系统性能的影响,提高了设计的成功率。

3.3 控制单元的设计

控制器本质上是一个结构及状态转移非常复杂的有限状态机(FSM)。从程序执行的宏观角度看,每一条指令对应着这个复杂的有限状态机的一个状态,一条一条指令的依次执行,就是一系列状态转移。控制器的实现主要有两种:硬布线实现方式和微程序实现方式。考虑到本次设计的是一个用于SOC的IP核所以采用PLA技术,就是用存储技术实现硬布线逻辑,可以认为它是硬布线逻辑控制器和微程序控制器两者的折衷方案。由于PLA微控制器集中了硬布线逻辑控制器与微程序控制器两者的优点,与硬布线逻辑控制器相比,它的设计工作量小,修改、维护都比较方便。与微程序控制器相比,它的速度较快。这些优点都适合其作为内核整合在SOC中。为了提高FSM的效率,我们把控制单元中组合逻辑和时序逻辑分开设计,组合逻辑主要输出控制信号并且产生次态逻辑,时序逻辑主要实现存储单元的读写。

评论