单片机多机冗余设计及控制模块的VHDL语言描述

本文提出一种表决式单片机多机冗余设计方案。该方案不同于中央系统的多机冗余设计。大规模系统冗余大多采用完善而复杂的机间通讯协议实现系统重构,不太注重系统的实时性。本方案结构简单,易于实现,具有极强的实时性,没有电子开关切换总线的咔嗒声输出。单片机价格低廉、功能灵活,也使得该设计在类似仪器仪表的小系统中的运用成为可能。

本文引用地址:https://www.eepw.com.cn/article/170680.htm1 设计原理

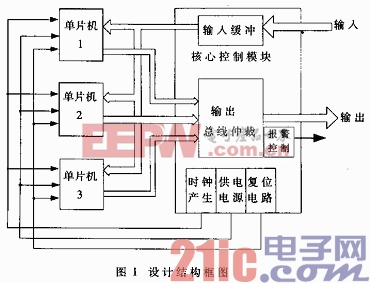

设计结构如图1所示。

完成整个冗余设计的电路被置于一个核心控制模块中,如果该模块以FPGA实现也就是一块芯片。图1中单片机1、2、3被假定为冗余的三个单片机,它们的输入总线并联,接收核心控制模块中输入缓冲的输出。输出总线分别接到模块的输出总线仲裁器。核心控制模块包括输入缓冲、输出总线仲裁、电源控制、时钟产生、复位电路和报警控制输出六个部分。

1.1 输入缓冲

为了消除输入端并联输入阻抗带来的影响,在输入端增加了一级缓冲器,减小外围电路的影响。采用输入缓冲,可以实现单片机和外围电路的输入隔离。

1.2 输出总线仲裁

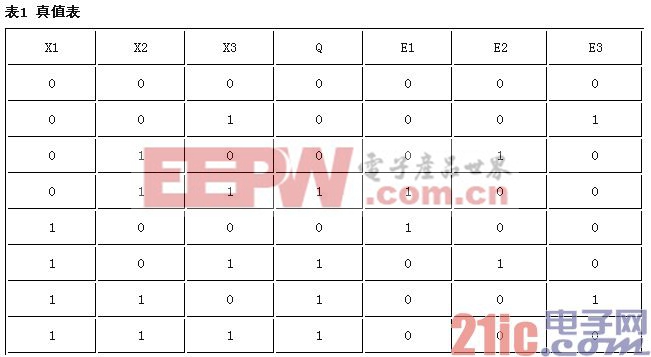

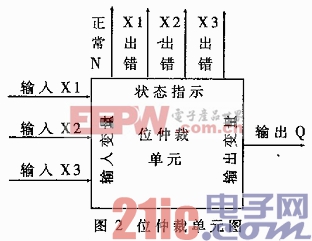

该总线仲裁是建立在所有单片机在时钟级上同步的基础上,通常采用总线表决法。即相同输出总线上的值作为仲裁的结构输出,不同输出总线被当作出错而封止,所有的输出皆不相同同是失败状态,无表决输出。表决的实现当然不能采用软件比较,以三个单片机系统的一位为例介绍表决方法。假设位输入变量X1、X2、X3,输出Q,状态指示:正常N、X1出错E1、X2出错E2、X3出错E3。真值表如表1所示,位仲裁单元如图2所示。

显然以上位单片机用数字电路难实现,后面给出整体的VHDL语言描述。总线仲裁由多个这样的位单元组成,个数由单片机输出总线的最大数n决定。仲裁器除了n根输出线,同时还对每个位单元的状态位进行逻辑组合输出正常、出错、失败三个状态指示。失败信号也用作报警保护控制输出,或重新复位输出。失败输出有效时输出失效。

以三个单片机的系统为例,如果将仲裁器的三个总线某一时刻输入看作为n位二进制变量X,Y,Z。如果X,Y,Z在任何时钟都逐位相同,而系统处于正常工作状态。如果三者中有两个变量逐位相同,而另一个不同,则系统处于出错状态。如果三者皆不相则系统失败。正常和出错状态可以运行,而失败状态必须保护和处理。

FPGA技术的发展,使得设计中的比较、决策等数字电路的设计实现变得非常容易,而且系统简明可靠。如果采用中规模集成电路来实现的话,将相当烦琐和复杂。

1.3 单片机时钟级同步的实现

系统的所有单片机必须达到时钟级的同步。单片机选用相同的型号(可以是不同的厂家),完全相同的程序和同一机器时钟。

同一时钟是实现时钟同步的第一步。时钟发生电路在控制模块内产生并送到各单片机的时钟输入端,要求单片机可外接时钟输入。时钟同步并不容易,以89C51为例,51系列单片机上电后振荡器起振输出,ALE脉冲由时钟经分频电路得到,一旦形成,机器周期脉冲和时钟脉冲相位关系固定,不受复位电路影响,直到电源掉电为止。

第二步是实现机器周期脉冲同步。MCS51一个机器周期包括6个状态周期,每个状态周期包括2个节拍,对应2个时钟节拍有效期。也就是说一个机器周期包括12个振荡周期,指令工作在时钟节拍上,同时更是同步工作在机器周期上。不论是单字节指令还是双字节指令,指令周期均是机器周期的1、2、4倍。要同步单片机节拍,必须同步机器周期。考虑到上电时间上可能产生的差异,采用先上电后加时钟脉冲的方法。上电时确保时钟输入端没有干扰脉冲引入,所有单片机上电后的内部分频电路起始点一致,然后加入时钟脉冲,各单片机获得同步的机器周期。

第三步是同步指令周期。指令的同步需要依靠复位电路来实现。在时钟脉冲正常输入和分频电路正常工作的情况下,复位操作是在复位端加上至少2个机器周期的复位电平而实现的。复位信号由核心控制器发出送至每片单片机。复位后,统一了片内主要寄存器内容,所有单片机程序从起始位置开始执行。

单片机时钟级同步的实现主要依靠电源控制、时钟产生、复位电路三部分硬件。

单片机相关文章:单片机教程

单片机相关文章:单片机视频教程

单片机相关文章:单片机工作原理

热敏打印机相关文章:热敏打印机原理

评论