MP3解码的IMDCT硬件加速器方案

关键词 MP3 IMDCT 硬件加速器 解码

MPEG-l/2 Audio Layer 3(简称MP3),是专门针对音乐和语音数据进行设计的有损压缩算法。在市场需求的推动下,会有越来越多的嵌入式系统支持MP3应用。因此,如何在嵌入式系统中利用有限的计算能力实现MP3的实时解码,成为值得关注的问题。MP3解码算法流程主要包括:帧同步和边带信息解码、Huffman解压缩、反量化、立体声解码、反锯齿、IMDCT和子带合成运算等。解码软件效率评估得到的数据表明,IMDCT过程的运算量占到了整个解码运算总量的19%,由此设想在系统级芯片内部添加一小块专用电路,专门负责处理MP3解码过程中IMDCT部分的运算。我们把这一小块专用电路称为“IMDCT硬件加速器”。将这部分代码通过硬件实现,并以硬件速度执行这些运算,可以有效地提高系统的解码性能。

本文采用软硬件协同设计的方法,提出了一种针对IMDCT运算的硬件加速器方案,目的在于使MP3解码过程中的速度和成本这两大要素得到优化。

1 IMDCT运算

MP3解码算法中使用反向修正离散余弦变换IMDCT(Inverse Modified Discrete Cosine Transform)将输入数据从频域变换到余弦域,对子带滤波进行补偿运算,如下式:

式中:在长窗类型帧中n取36;在短窗类型帧中n取12。

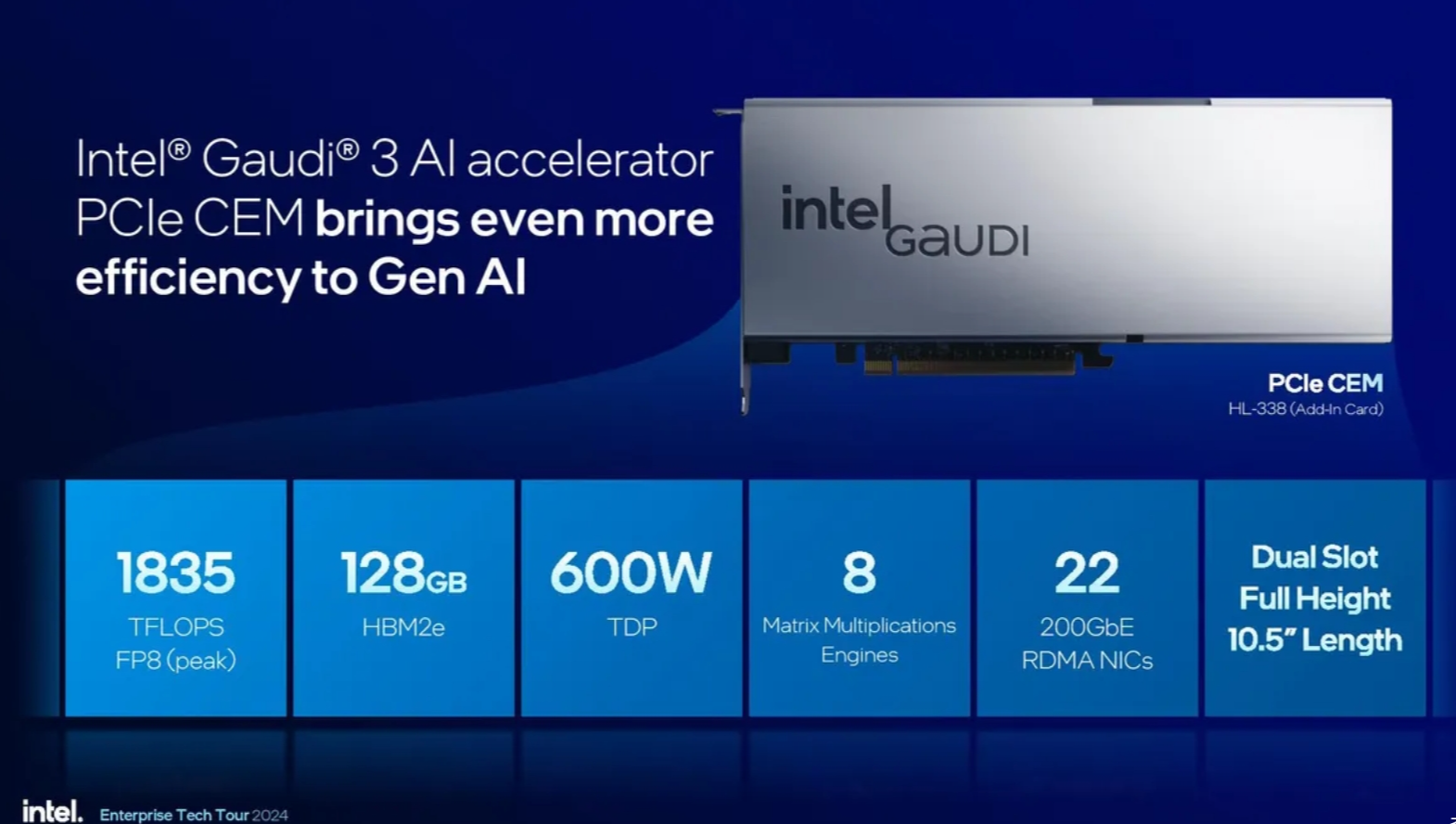

完成IMDCT变换后,结果xi必须再与视窗函数Wi作乘积运算。视窗函数是由边带信息中bllk_type位的值来确定的。长窗类型叉可以根据帧首部定义进一步划分为aormal、start、stop三种子类型,IMDCT变换得到36个结果数据;而在短窗类型下,MP3解码器将执行3次IM-DCT变换产生12个输出结果,然后互相叠加补零后也得到36个数据,类似于长窗类型的输出结果。将这36个数据与上一次的结果进行叠加,得到IMDCT变换的18个最终输出结果。音频数据分单声道和双声道,包含若干颗粒;每个颗粒有576个数据项,共包括32个数据块,需要分别进行IMDCT变换。一个颗粒变换完成后,经过较为简单的频率反转后得到的18个子带(每个子带包含32个数据)即可作为子带合成的输入信息。我们把从18项输入数据到18项输出数据的整个过程(包括IMDCT变换、数据加窗运算、叠加)称为“IMDCT运算”,如图1所示。本文所讨论的IMDCT硬件加速器,即实现这部分功能的专用电路。

2 IMDCT变换算法的选择

ISO标准解码代码里,IMDCT变换的算法没有进行优化。当式(1)中n=12时,做一次IMDCT需要72次乘法和66次加法;n=36时,做一次IMDCT需要648次乘法和630次加法。可见,IMDCT变换占用了大量的CPU时间,成为MP3解码过程中主要的性能瓶颈之一。将IMDCT做成硬件加速模块,也需要使用更快速的IMDCT算法,以进一步提高速度。这里引入一种新型的IMDCT算法。运用这种算法,当式(1)中n=12时,做一次IMDCT只需13次乘法和39次加法;n=36时,做一次IMDCT需要47次乘法和165次加法(详见参考文献)。同时,采用余弦查找表来代替实际的cos()函数运算,以加快长窗下的cos 36和短窗下的cos 12的变换速度。IMDCT算法改进后,运算过程得到简化,乘法数量大大减少,从而提高了系统性能。

3 叠加运算的优化

速度和成本是设计的两大要素。考虑到硬件成本,IMDCT硬件单元的面积应受到严格控制。这里提出一种叠加运算的优化算法,利用该算法,可以节省23118个字的存储电路单元。下面对此优化算法进行详细介绍。

IMDCT运算的主要数据结构如下:

可以看到,对于双声道立体声数据(stereo=2),常见的算法是对前一区块2个颗粒(共23218个数据项)进行IMDCT运算,保存23218个字的高18项数据,再对下一区块的23218个数据项进行IMDCT运算,将得到的23218个字的低18项数据与之前保存的上一区块的高18项数据相叠加,得到输出结果。将IMDCT运算的数据叠加部分用硬件实现时,需要一块大小为23218个字的存储电路(prevbuf[2][32][18])来存储高18项数据,用于下一步的叠加运算。对嵌入式SoC来说,降低存储电路的需求意味着减小芯片面积。于是采用软硬件协同设计的方式对算法进行改进,通过改变IMDCT运算所需数据的输入次序,相对减少IMDCT变换输出数据的量。如此一来,有效地减少了硬件加速器的存储单元,减小了电路面积。

首先,在解码软件里,完成2个区块4个颗粒数据的反锯齿运算,并将结果存储到一片连续的内存区域内。具体做法如下:

然后,采用交错读取数据的方法,先将处在区块相同位置、需要进行叠加的子带进行IMDCT运算。这样,可以将存储中间结果的prevbuf缩小到218个字,大大降低了对存储单元的需求,减小了电路面积。具体实现如下:

4 硬件实现

由图l可知,IMDCT运算主要包含3部分:IMCCT变换、数据加窗运算以及叠加运算。IMDCT变换部分主要是把由反锯齿运算得到的数据IN与cos系数相乘和累加,并把最后的结果放入寄存器SUM中;加窗运算是把计算好的SUM与加窗系数Wi相乘;叠加部分则是将加窗运算后的数据进行叠加。总体结构图如图2所示。

由图2可知,通过合理的流程设计和利用多路选择器(MUX),整个硬件加速器只需要1个乘法器和1个加法器,大大降低了通过硬件实现IMDCT运算的成本。

结 语

本文通过引进新的IMDCT变换算法,优化IMDCT运算过程中的叠加运算,加快了整体的运算速度,降低了对存储单元的需求,为高速度、低成本地实现IMDCT硬件加速器提供了一种方案。

评论